A

# **Course File**

On

# "COMPUTER ORGANIZATION AND ARCHITECTURE"

# **Submitted by**

# Dr. Nidamanuru Srinivasa Rao Associate Professor

In the Department of

Computer Science and Engineering

NARSIMHA REDDY ENGINEERING COLLEGE (UGC-AUTONOMOUS)

(Affiliated to J.N.T.U, HYDERABAD)

MAISAMMGUDA (V), DHULAPALLY (P), MEDCHAL (M) SECUNDERABAD-500100 (2022-2023)

## **COURSE FILE**

Program Name : B.Tech- Computer Science and Engineering

Name of the Course : COMPUTER ORGANIZATION AND ARCHITECTURE

Course Code : CS2104PC

Year & Semester : II– B.Tech- I SEM

| S.NO | CONTENTS                                                                                                                                                                                                                    | Included |  |  |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|--|--|

| 1    | Department Vision & mission, PEOs ,PSOs and POs                                                                                                                                                                             | YES      |  |  |  |

| 2    | Academic Calendar                                                                                                                                                                                                           | YES      |  |  |  |

| 3    | Syllabus                                                                                                                                                                                                                    | YES      |  |  |  |

| 4    | CO/PO Mapping                                                                                                                                                                                                               | YES      |  |  |  |

| 5    | Nominal Rolls of the Students                                                                                                                                                                                               | YES      |  |  |  |

| 6    | Time Table                                                                                                                                                                                                                  | YES      |  |  |  |

| 7    | Lesson Plan                                                                                                                                                                                                                 | YES      |  |  |  |

| 8    | Unit Wise question Bank                                                                                                                                                                                                     | YES      |  |  |  |

| 9    | Old Question Papers                                                                                                                                                                                                         | YES      |  |  |  |

| 10   | Question Papers (CIA & SEE)                                                                                                                                                                                                 | YES      |  |  |  |

| 11   | Tutorial Sheets                                                                                                                                                                                                             | YES      |  |  |  |

| 12   | Learning Methodologies: Experiential learning (Industrial Visits, Internships, Mini Projects, Academic Projects, Guest Lectures, Students workshops etc), Problem Solving Methodologies (Assignment, Quiz, Case study etc.) | YES      |  |  |  |

| 13   | Subjects Notes/PPTs/Self study material. YES                                                                                                                                                                                |          |  |  |  |

| 14   | Feedback on curriculum design and development YES                                                                                                                                                                           |          |  |  |  |

| 15   | CO/PO attainment, analysis and action taken report YES                                                                                                                                                                      |          |  |  |  |

#### 1. Department Vision & Mission

#### **Vision of the Department:**

To evolve as a center of excellence with international reputation by adapting the rapid advancements in the computer specialization fields.

### **Mission of the Department:**

- 1. To provide a strong theoretical and practical background in the area of computer science with an emphasize on software development

- 2. To inculcate Professional behavior, strong ethical values, leadership qualities, research capabilities and lifelong learning.

- 3. To educate students to be effective problem solvers, apply knowledge with social sensitivity for the betterment of the society and humanity as a whole.

# 2. List of PEOs, POs & PSOs PEOs:

- 1. PEO-I: To provide students with a solid foundation in mathematics, engineering, basic science fundamentals required to solve computing problems and also to pursue higher studies and research.

- 2. PEO-II To train students with good Computer Science and Engineering breadth so as to comprehend, analyze, design and create innovative computing products and solutions for real life problems.

- **3.** PEO-III To inculcate in students professional and ethical attitude, communication skills, teamwork skills, multi-disciplinary approach and an ability to relate computer engineering issues with social awareness.

#### POs:

| 1 | <b>PO1. Engineering knowledge:</b> Apply the knowledge of basic sciences and fundamental engineering concepts in solving engineering problems.                                  |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | engineering concepts in solving engineering problems.                                                                                                                           |

| 2 | <b>PO2. Problem analysis:</b> Identify and define engineering problems, conduct experiments and investigate to analyze and interpret data to arrive at substantial conclusions. |

|   |                                                                                                                                                                                 |

|   | <b>PO3.</b> Design/development of solutions: Propose an appropriate solution for engineering problems complying with functional constraints such as economic,                   |

| 3 | environmental, societal, ethical, safety and sustainability.                                                                                                                    |

|   | PO4. Conduct investigations of complex problems: Perform investigations, design and                                                                                             |

| 4 | conduct experiments, analyze and interpret the results to provide valid conclusions.                                                                                            |

|   | PO5. Modern tool usage: Select or create and apply appropriate techniques and IT tools                                                                                          |

| 5 | for the design & analysis of the systems.                                                                                                                                       |

|   | PO6. The engineer and society: Apply reasoning informed by the contextual                                                                                                       |

| 6 | knowledge to assess societal, health, safety, legal and cultural issues and the consequent                                                                                      |

|   | responsibilities relevant to the professional engineering practice.                                                                                                             |

| 7 | PO7. Environment and sustainability: Demonstrate professional skills and contextual                                                                                             |

|    | reasoning to assess environmental or societal issues for sustainable development.                                                                                                             |  |  |  |  |  |  |  |  |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 8  | <b>PO8. Ethics</b> : Apply ethical principles and commit to professional ethics and responsibilities and norms of the engineering practice.                                                   |  |  |  |  |  |  |  |  |

| 9  | <b>PO9.</b> Individual and team work: Function effectively as an individual, and as a member or leader in diverse teams, and in multi-disciplinary situations.                                |  |  |  |  |  |  |  |  |

| 10 | <b>PO10.</b> Communication: Communicate effectively among engineering community, being able to comprehend and write effectively reports, presentation and give / receive clears instructions. |  |  |  |  |  |  |  |  |

| 11 | <b>PO11. Project management and finance</b> : Demonstrate and apply engineering & management principles in their own / team projects in multidisciplinary environment.                        |  |  |  |  |  |  |  |  |

| 12 | PO12. Life-long learning: Recognize the need for, and have the ability to engage in independent and lifelong learning.                                                                        |  |  |  |  |  |  |  |  |

#### **PSOs:**

- 1. PSO1: To provide effective and efficient real time solutions using acquired knowledge in various domains to crack problem using suitable mathematical analysis, data structure and suitable algorithm

- 2. PSO2: To develop environmental and sustainable engineering solution having global and societal context using modern IT tools.

- 3. PSO3: To exhibit professional and leadership skills with ethical values dealing diversified projects with excellent communication and documentation qualities.

## 2. Academic Calendar:

## NARSIMHA REDDY ENGINEERING COLLEGE (UGC-AUTONOMOUS)

(Sponsored by Jakkula Educational Society)

Maisammaguda (V), Dhulapally Post, Near Kompally, Secunderabad - 500 100 Telangana

Ambabad to paties, Approved by ALTE, New Bolis, Courses According by Stat, And Will 'A' Grade, An IIO 1001; 2015 Governed Institution

## ACADEMIC CALENDAR FOR B.TECH II YEAR I SEMESTER FOR THE AY 2022-23

| S.No.  | Description                                               | Dur        | Duration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |

|--------|-----------------------------------------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 100000 | Description                                               | From       | To                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | (Weeks) |

| 1      | Commencement of I Semester class work                     | 28-09      | -2022                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |

|        | 1st Spell of Instructions (Including Dussera<br>Vacation) | 28-09-2022 | 26-11-2022                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9       |

| 3      | First Mid Term Examinations                               | 28-11-2022 | 03-12-2022                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1       |

| 4      | Submission of Mid-I Marks                                 | 07-12      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |

| 5      | Parent-Teacher Meeting                                    | 10-12      | -2022                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |

| 6      | 2 <sup>nd</sup> Spell of Instructions                     | 05-12-2022 | 28-01-2023                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8       |

| 7      | Second Mid Term Examinations                              | 30-01-2023 | 04-02-2023                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1       |

| 8      | Submission of Mid-II Marks                                | 07-02      | Children Code Code (Code |         |

| 9      | Preparation Holidays & Lab Examinations                   | 06-02-2023 | 11-02-2023                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1       |

| 10     | End Semester Examinations                                 | 13-02-2023 | 25-02-2023                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2       |

|        |                                                           |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |

# ACADEMIC CALENDAR FOR B.TECH II YEAR II SEMESTER FOR THE AY 2022-23

| S.No. | Description                                                                 | Dura       | ation                 |     |

|-------|-----------------------------------------------------------------------------|------------|-----------------------|-----|

|       |                                                                             | From       | To                    |     |

| 1     | Commencement of II Somester class work                                      | 27-02      | -2023                 |     |

| 2     | 1st Spell of Instructions                                                   | 27-02-2023 | 22-04-2023            | 8   |

|       | First Mid Term Examinations                                                 | 24-04-2023 | 29-04-2023            | 1   |

| 4     | Submission of Mid-I Marks                                                   | 03-05      | -2023                 | -   |

| 5     | Parent-Teacher Meeting                                                      |            | -2023                 |     |

|       | 2 <sup>nd</sup> Spell of Instructions (Including 2 Week<br>Summer Vacation) | 01-05-2023 | 08-07-2023            | 10  |

| 7     | Second Mid Term Examinations                                                | 10-07-2023 | 15-07-2023            | -   |

| 8     | Submission of Mid-II Marks                                                  | 19-07      | Account to the second | -   |

| 9     | Preparation Holidays & Lab Examinations                                     | 17-07-2023 | 22-07-2023            | - 1 |

| 10    | End Semester Examinations                                                   | 24-07-2023 | 05-08-2023            | 2   |

- Chairman

- 2 IQAC

- 3. All HODs

- 4. Administrative Officer

- 5. Account officer

- 6. Web Portal I/C 7. ERP I/C

- 8. Library

- 9. Student Notice Boards

NAPASIMMA REDDY ENCINEERING COLLEGE Survey No: 518, Maisternagush (N), Jusquily (P) Medinal (M), Meachal Dist, Hydrosias-500100

#### 3. SYLLABUS:

#### COMPUTER ORGANIZATION AND ARCHITECTURE

| <b>Course Code</b>                                                             | Category Hours / Week Credits Ma |   |   |   | otther') |     | Max | Maximum Mark |  |

|--------------------------------------------------------------------------------|----------------------------------|---|---|---|----------|-----|-----|--------------|--|

| CS2104PC                                                                       | Core                             | L | T | P | C        | CIA | SEE | Total        |  |

| C521041 C                                                                      | Core                             | 3 | 0 | 0 | 3        | 30  | 70  | 100          |  |

| Contact classes: 60 Tutorial Classes: NIL Practical classes: NIL Total Classes |                                  |   |   |   | ses :60  |     |     |              |  |

| Prerequisites: No Prerequisites                                                |                                  |   |   |   |          |     |     |              |  |

#### **Course Objectives:**

- The purpose of the course is to introduce principles of computer organization and the basic architectural concepts.

- It begins with basic organization, design and programming of a simple digital computer and introduces simple register transfer language to specify various computer operations.

- Topics include computer arithmetic, instruction set design, micro programmed control unit, pipelining and vector processing, memory organization and I/O systems and multiprocessors

#### **Course Outcomes:**

- Understand the basics of instructions sets and their impact on processor design.

- Demonstrate an understanding of the design of the functional units of a digital computer system.

- Evaluate cost performance and design trade-offs in designing and constructing a computer processor including memory.

- Design a pipeline for consistent execution of instructions with minimum hazards.

- Recognize and manipulate representations of numbers stored in digital computers

#### **COURSE SYLLABUS**

#### **MODULE-I**

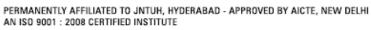

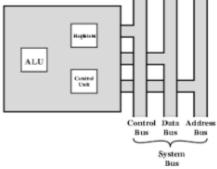

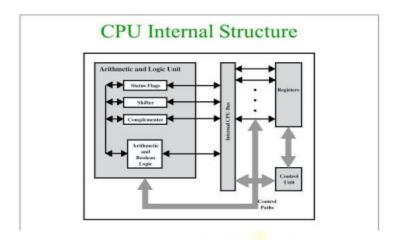

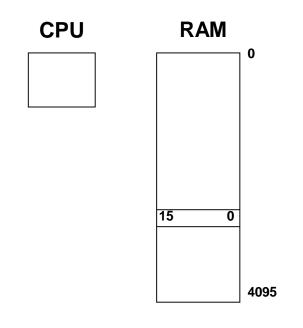

**Digital Computers:** Introduction, Block diagram of Digital Computer, Definition of Computer Organization, Computer Design and Computer Architecture.

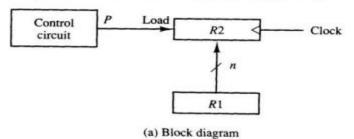

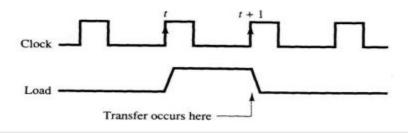

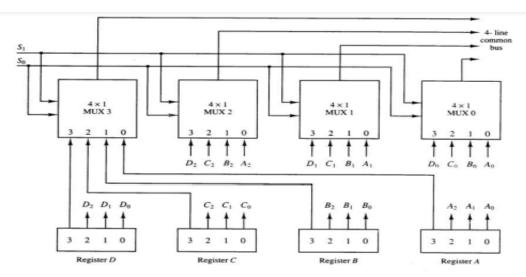

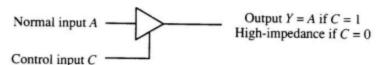

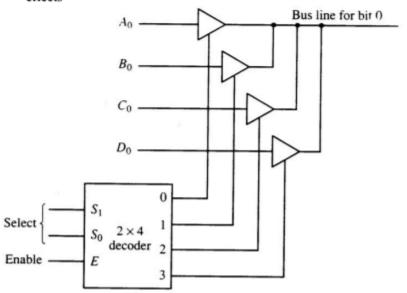

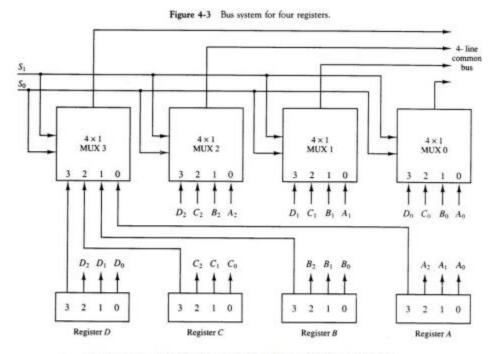

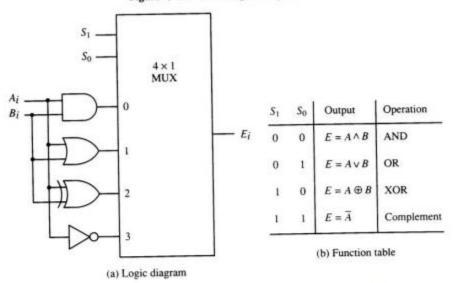

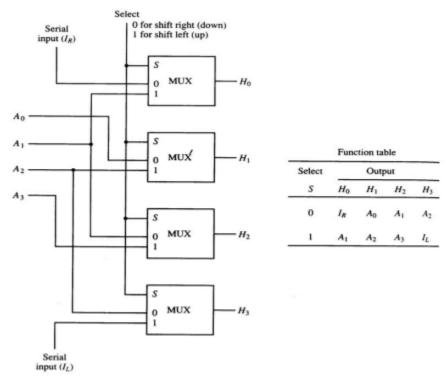

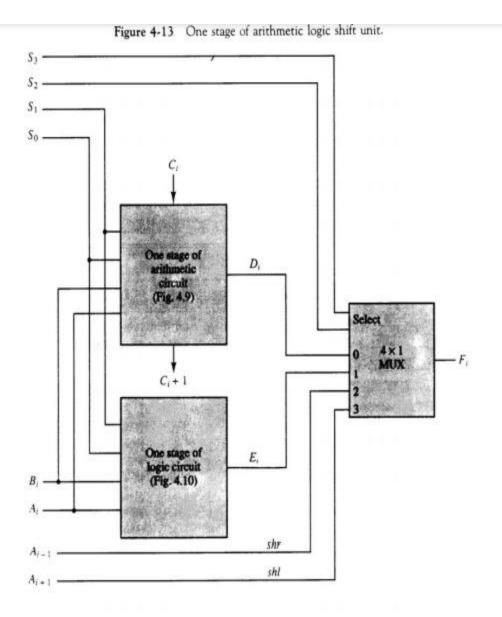

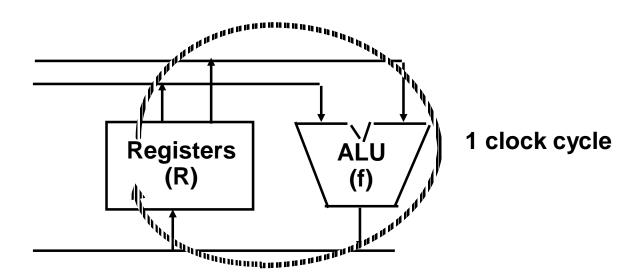

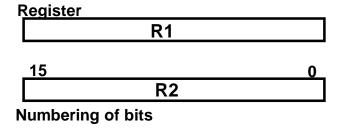

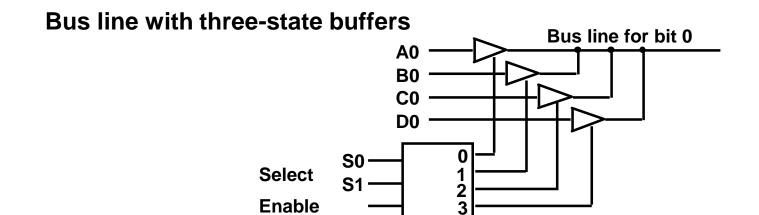

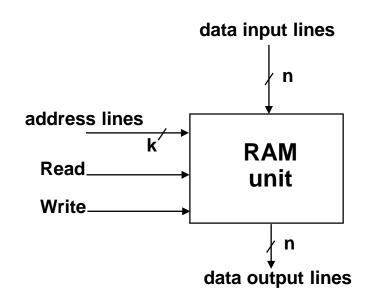

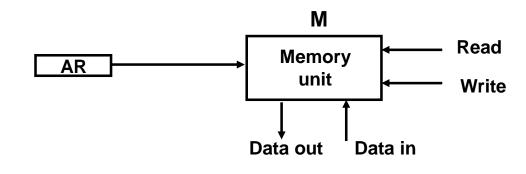

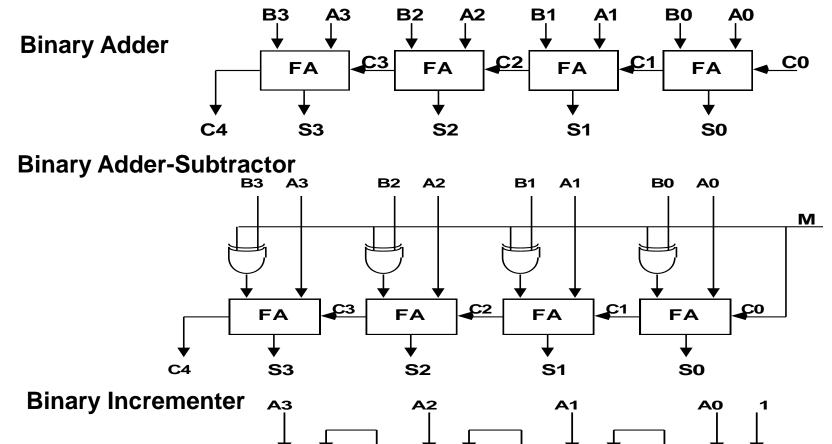

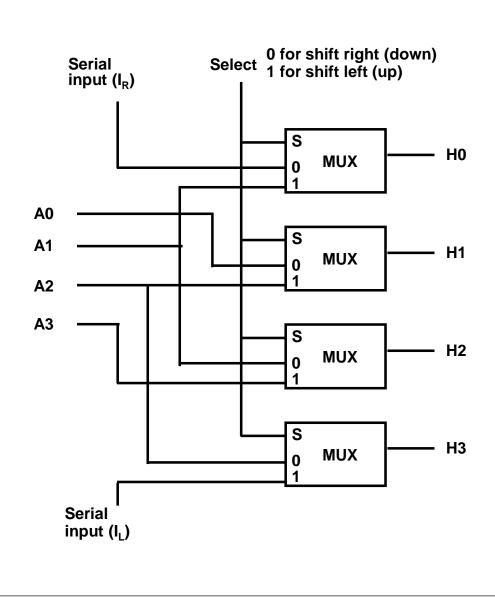

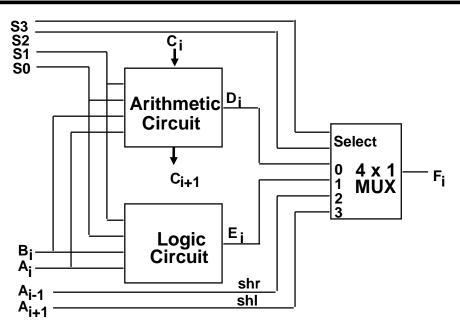

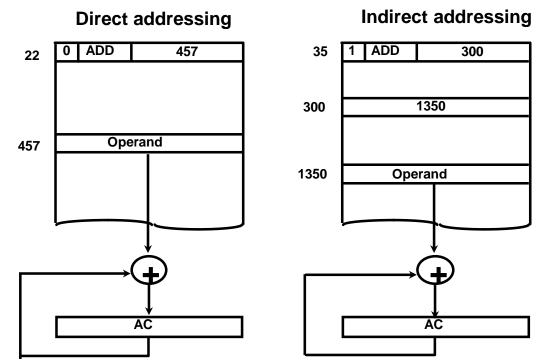

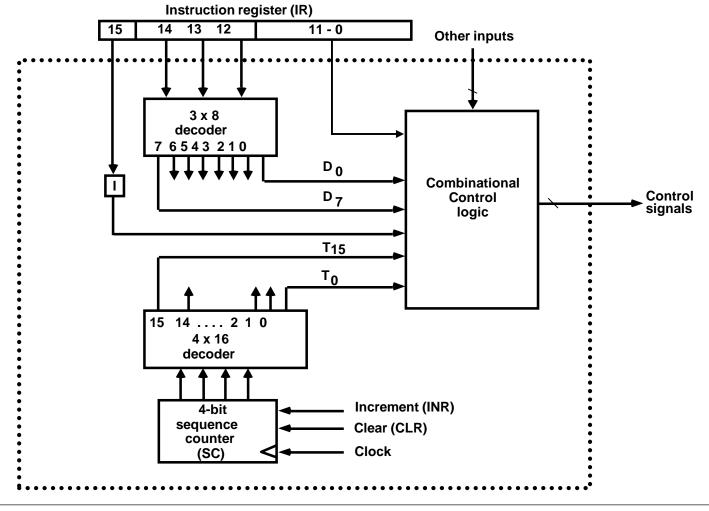

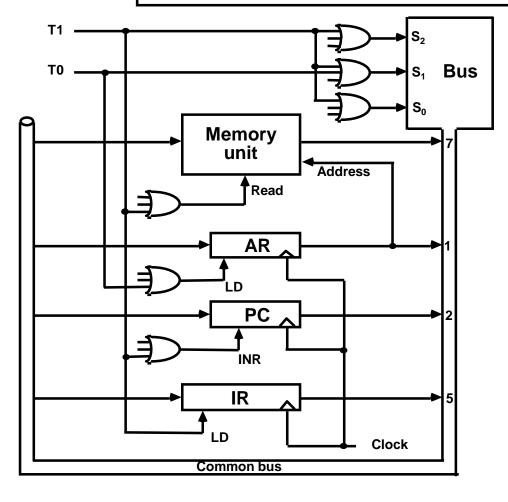

**Register Transfer Language and Micro operations:** Register Transfer language, Register Transfer, Bus and memory transfers, Arithmetic Micro operations, logic micro operations, shift micro operations, Arithmetic logic shift unit.

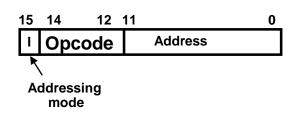

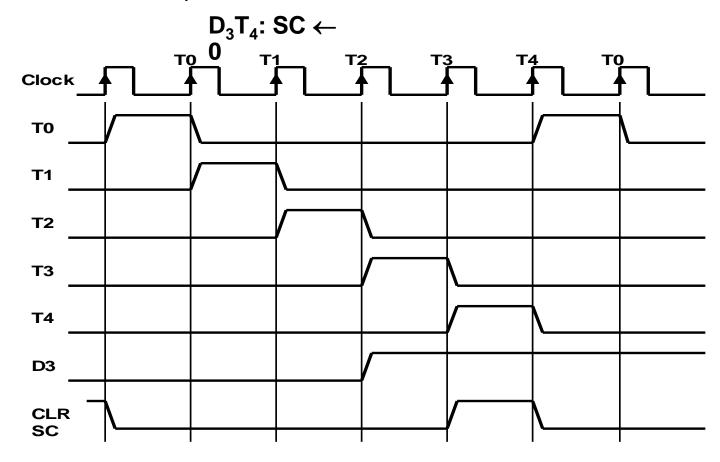

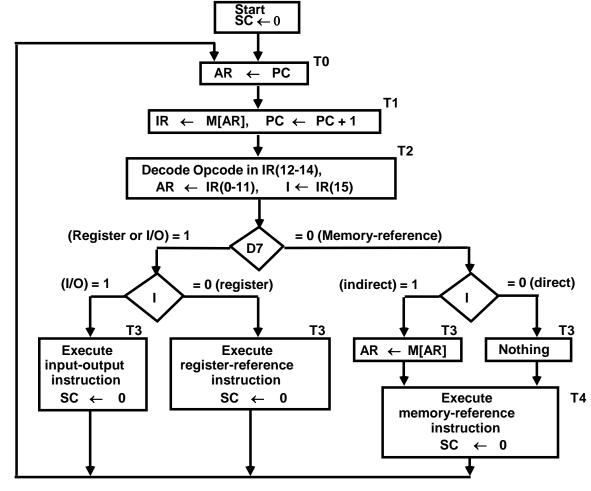

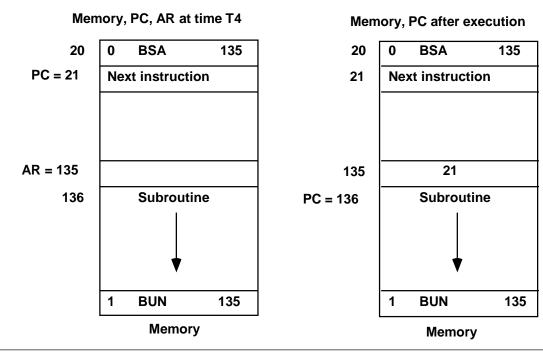

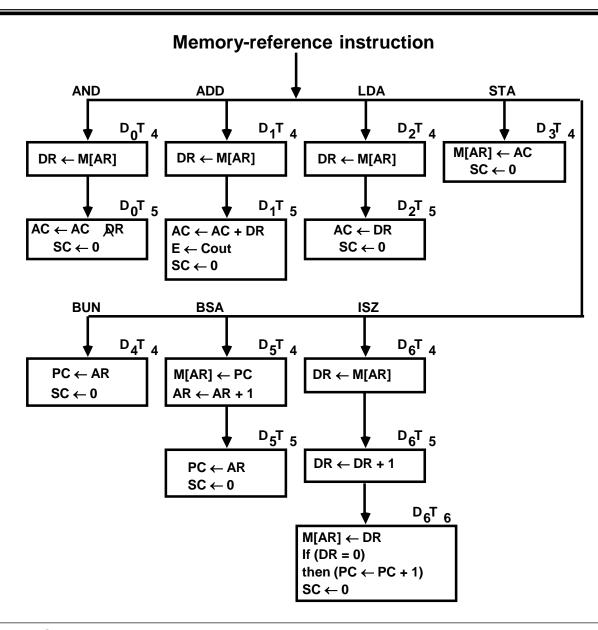

**Basic Computer Organization and Design:** Instruction codes, Computer Registers Computer instructions, Timing and Control, Instruction cycle, Memory Reference

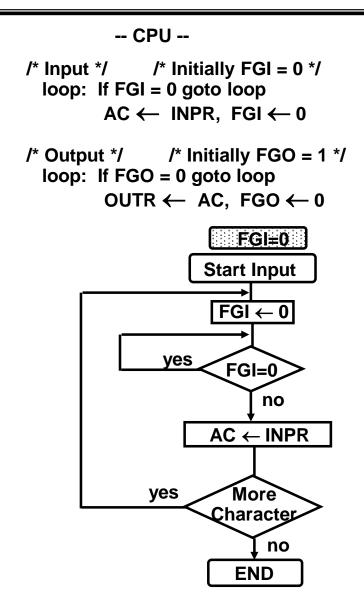

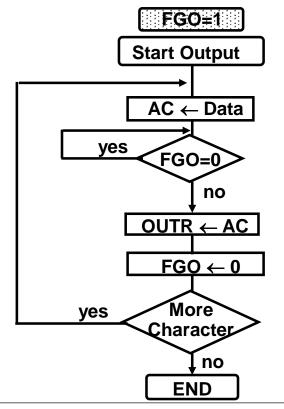

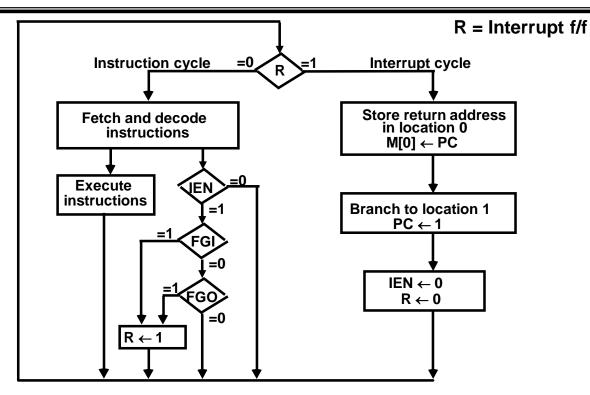

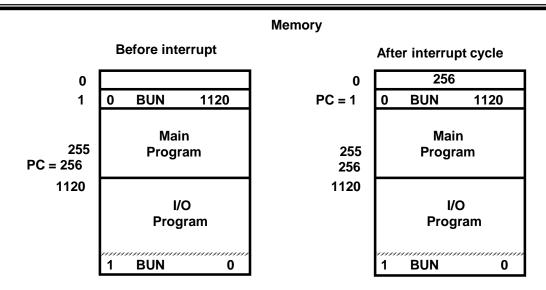

Instructions, Input – Output and Interrupt.

#### **MODULE-II**

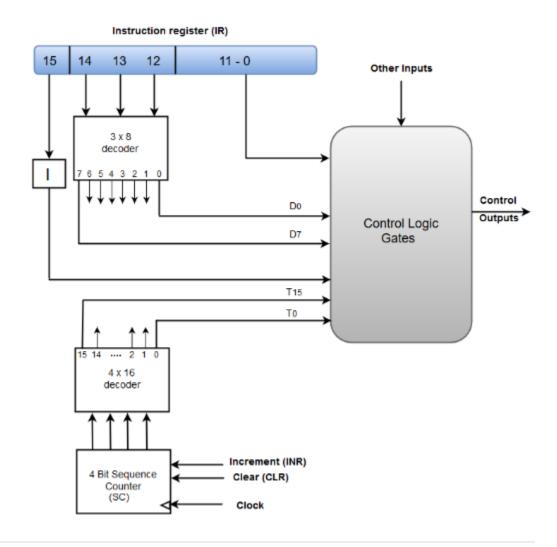

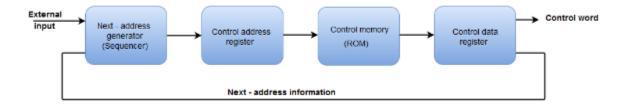

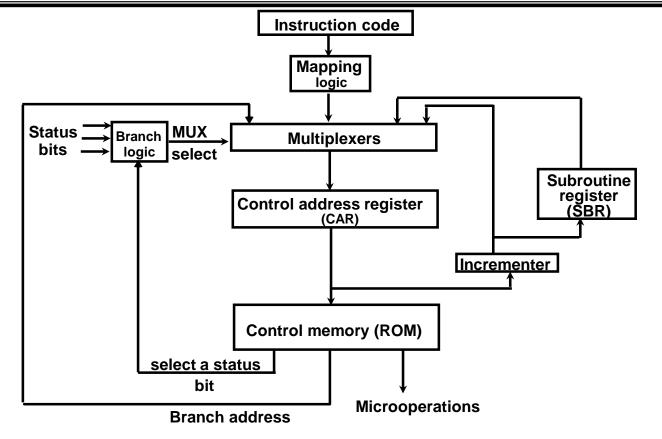

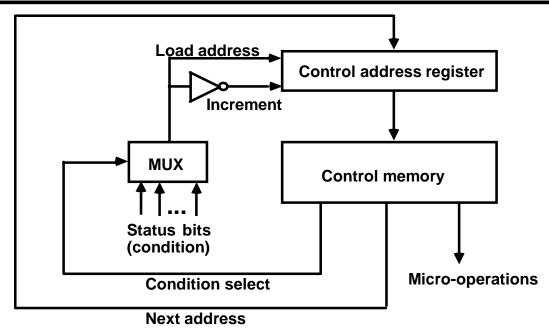

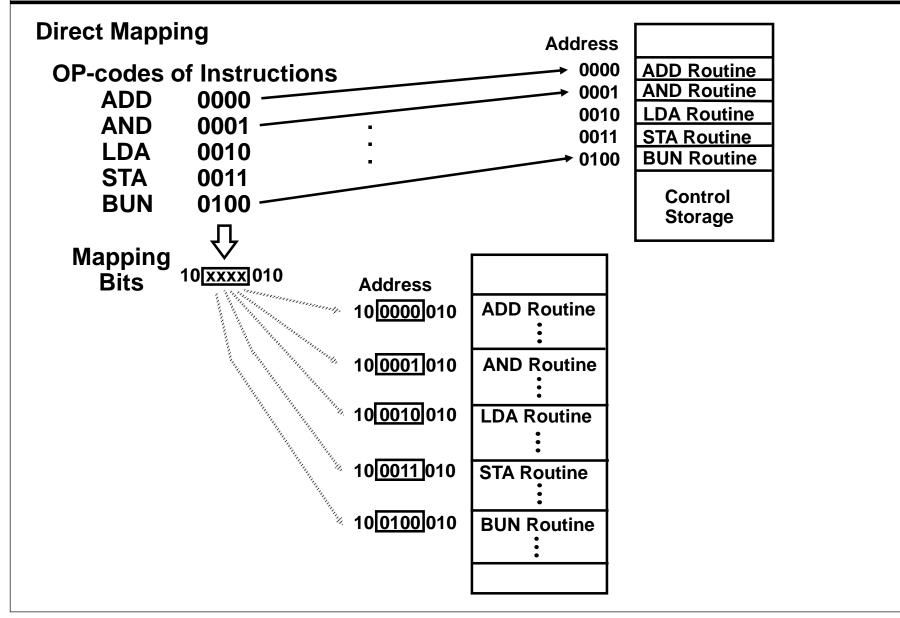

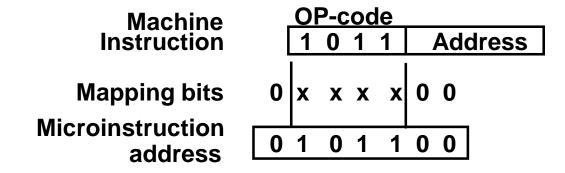

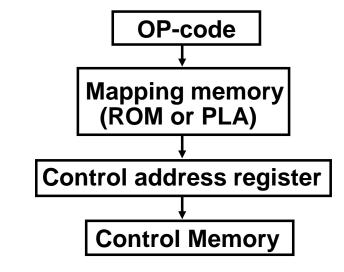

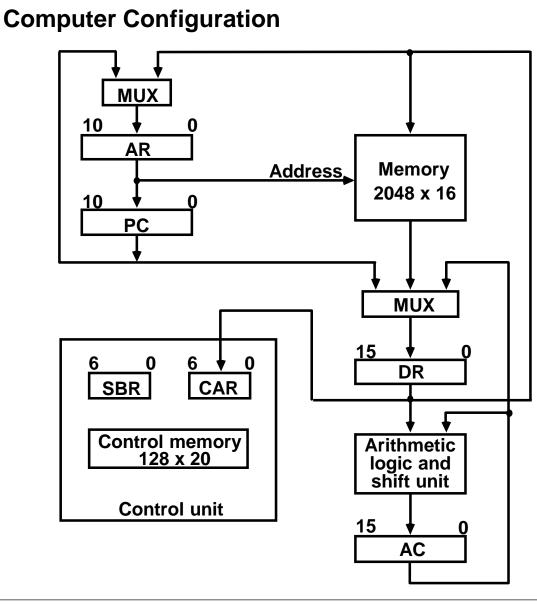

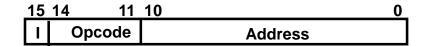

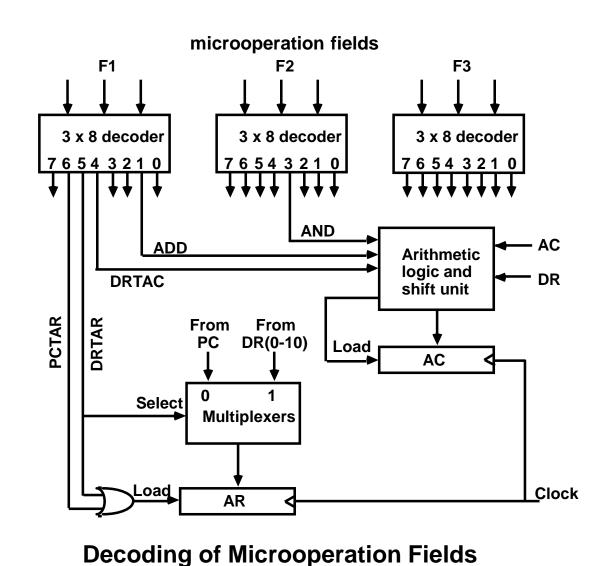

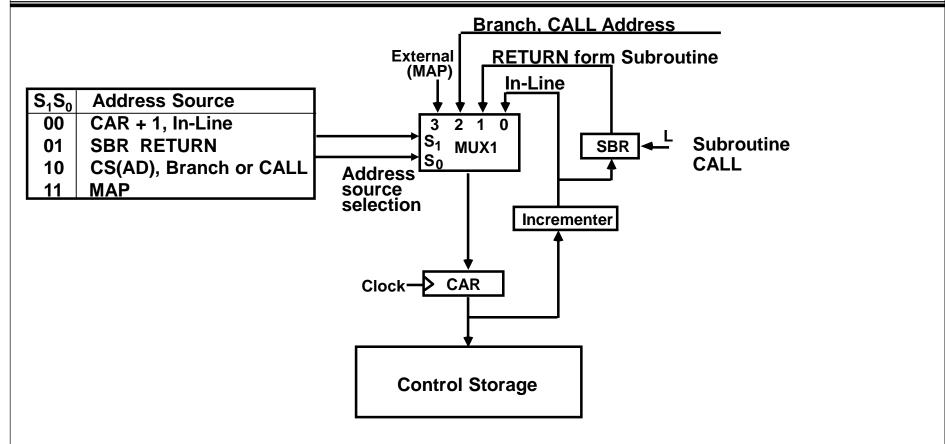

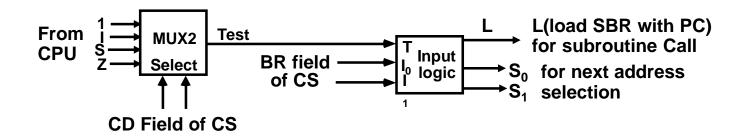

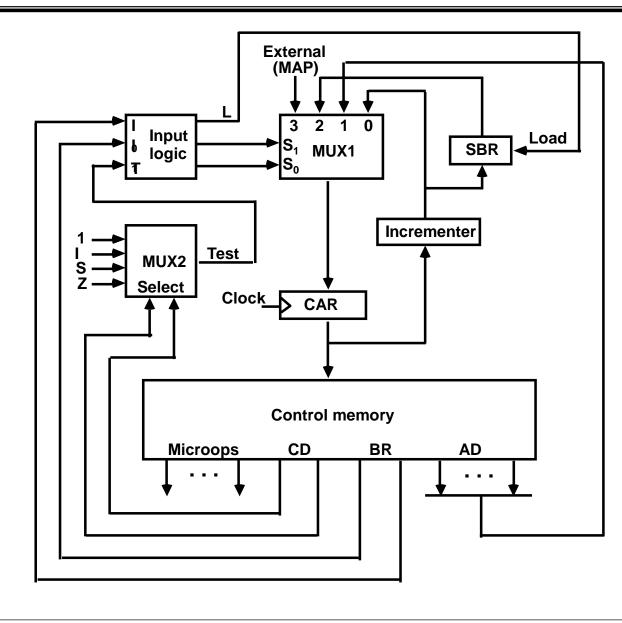

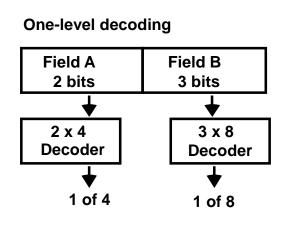

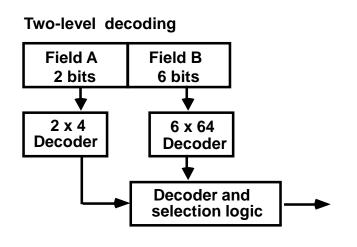

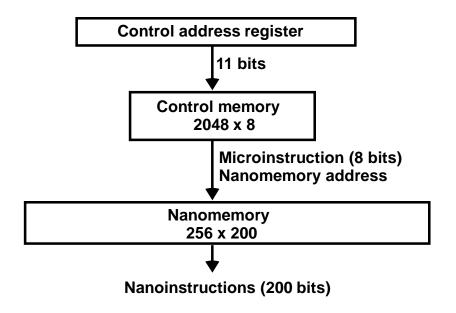

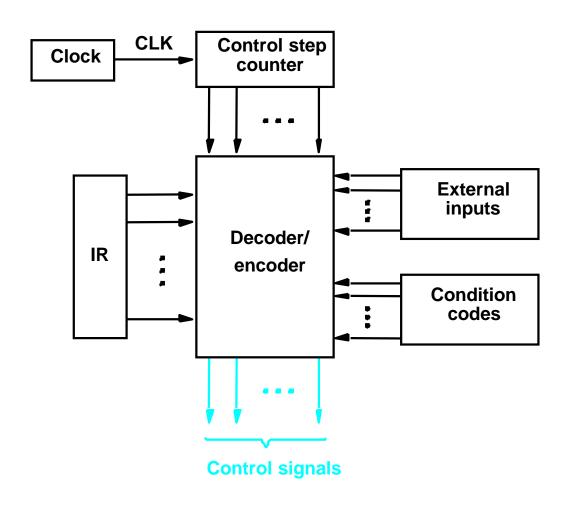

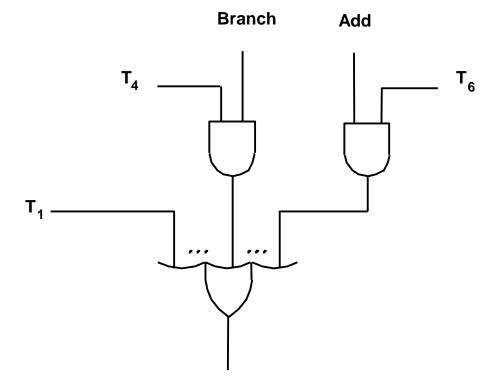

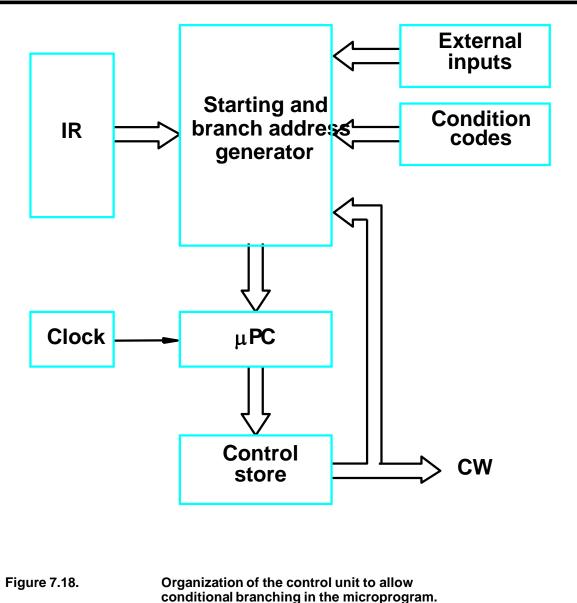

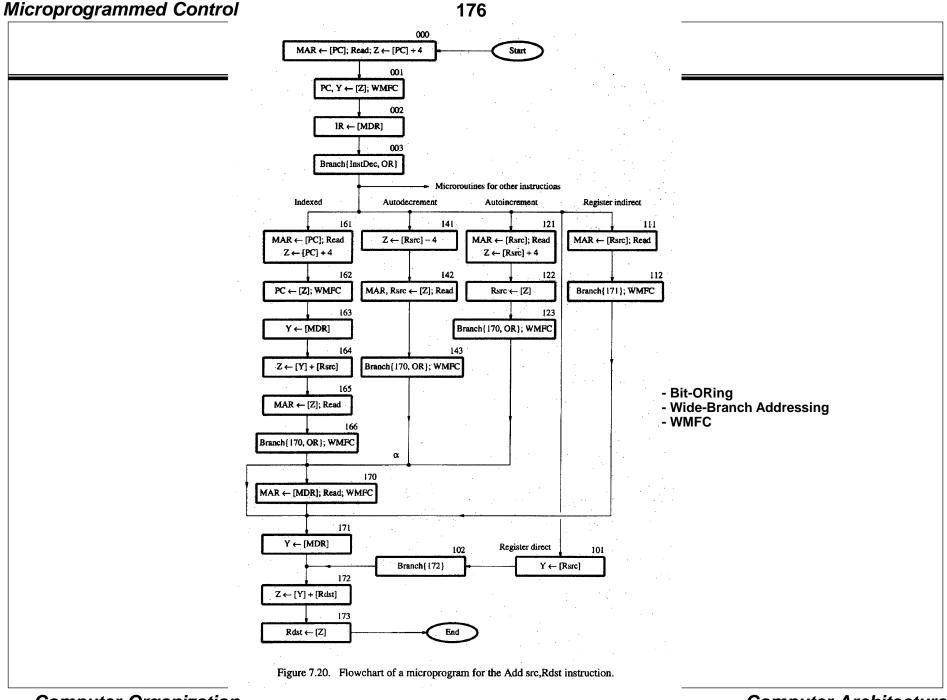

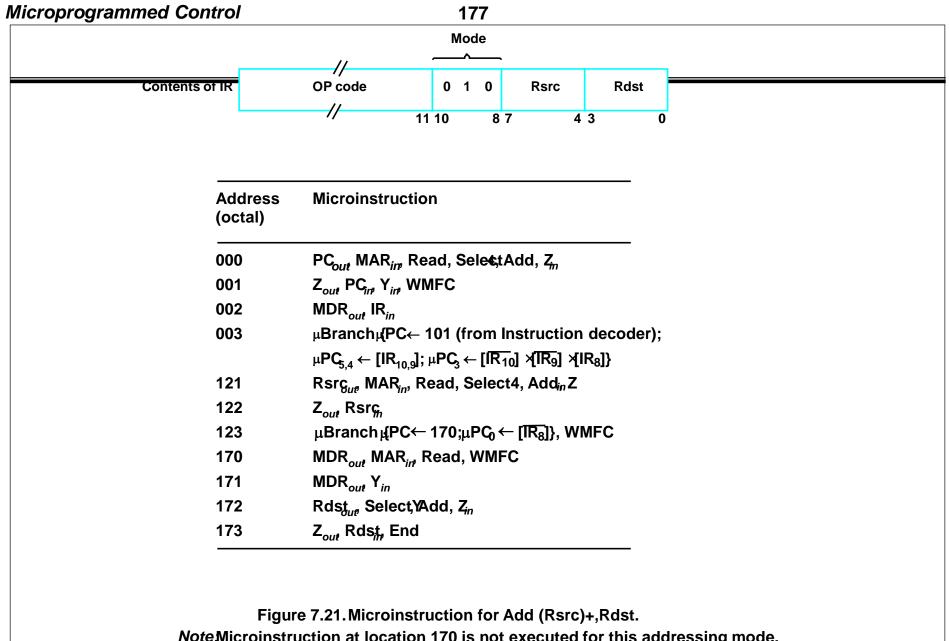

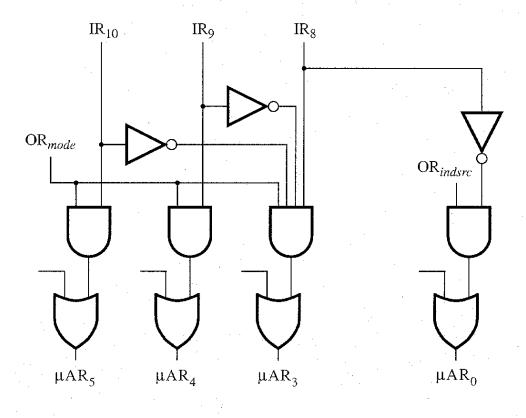

**Microprogrammed Control:** Control memory, Address sequencing, micro program example, design of control unit.

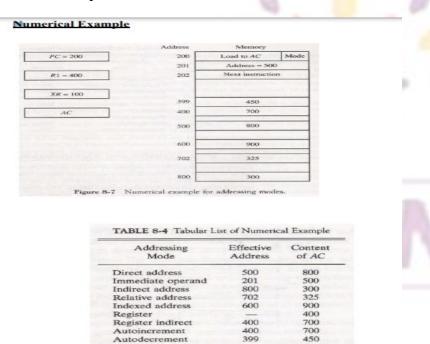

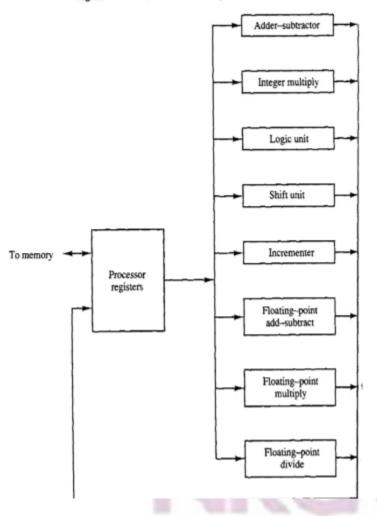

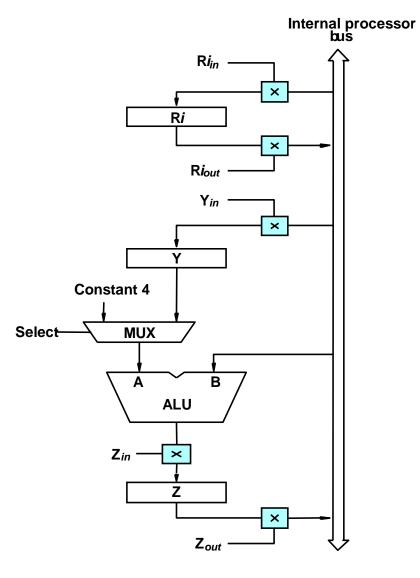

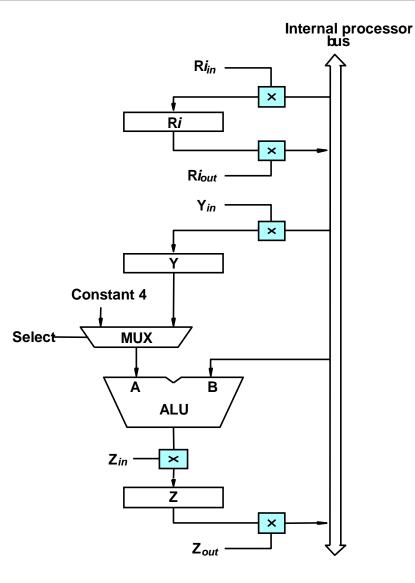

**Central Processing Unit:** General Register Organization, Instruction Formats, Addressing modes, Data Transfer and Manipulation, Program Control.

#### **MODULE-III**

**Data Representation:** Data types, Complements, Fixed Point Representation, Floating Point Representation.

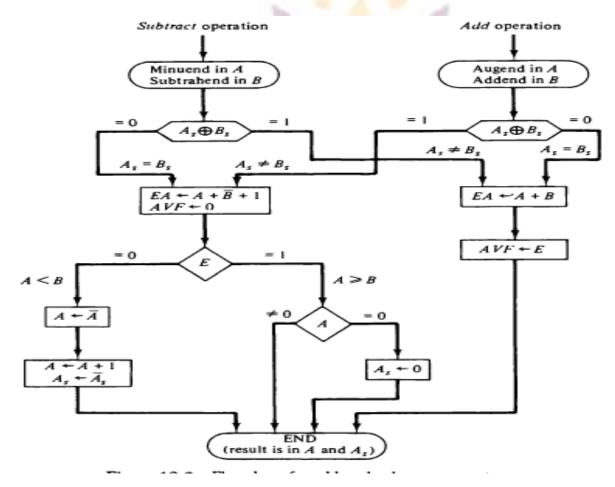

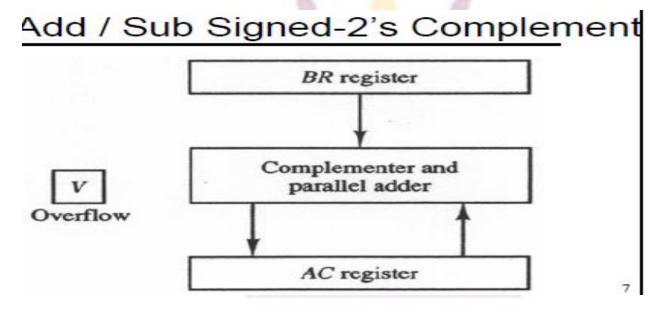

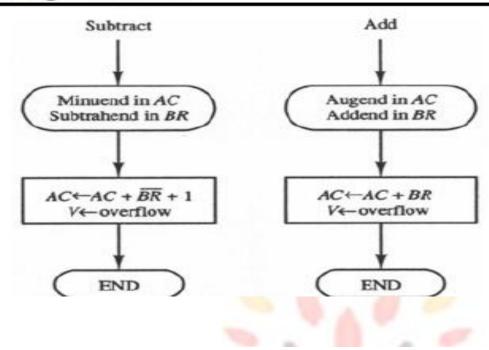

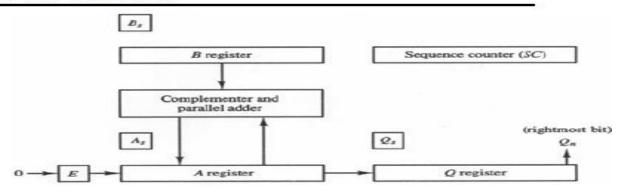

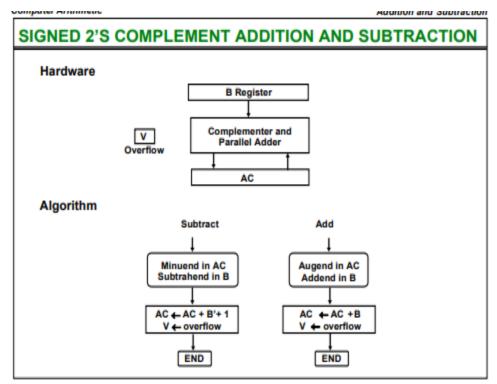

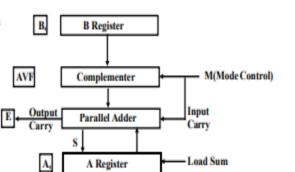

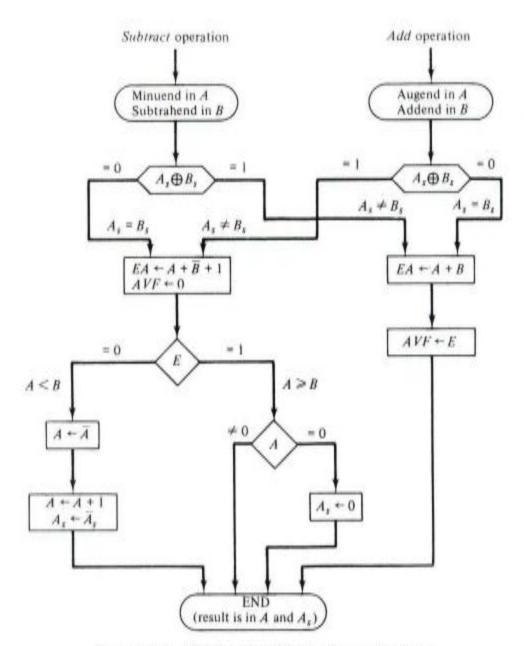

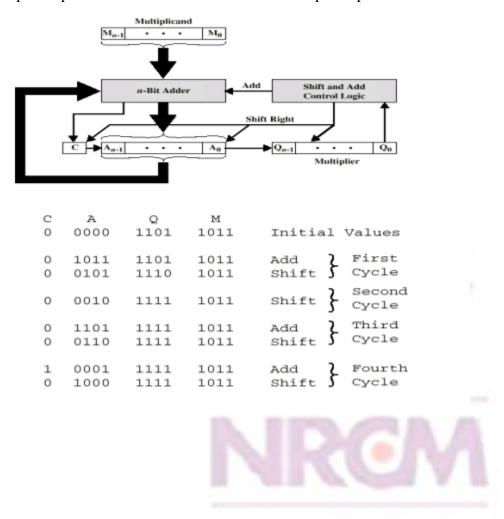

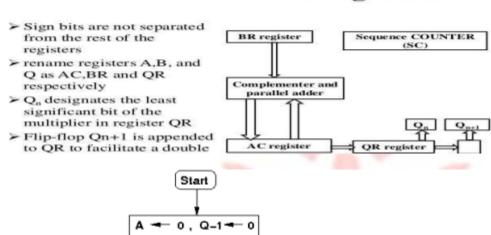

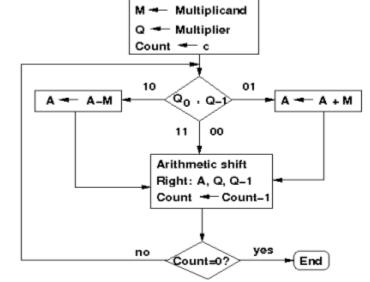

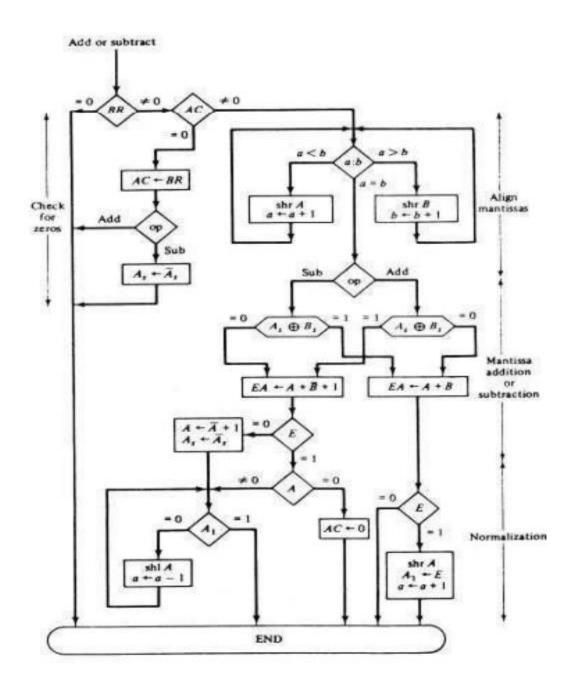

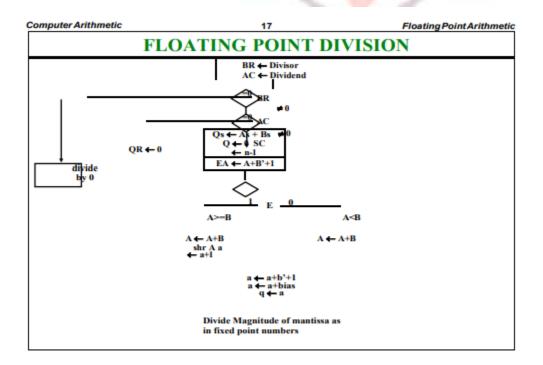

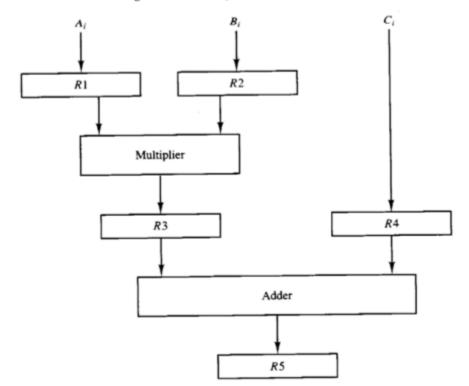

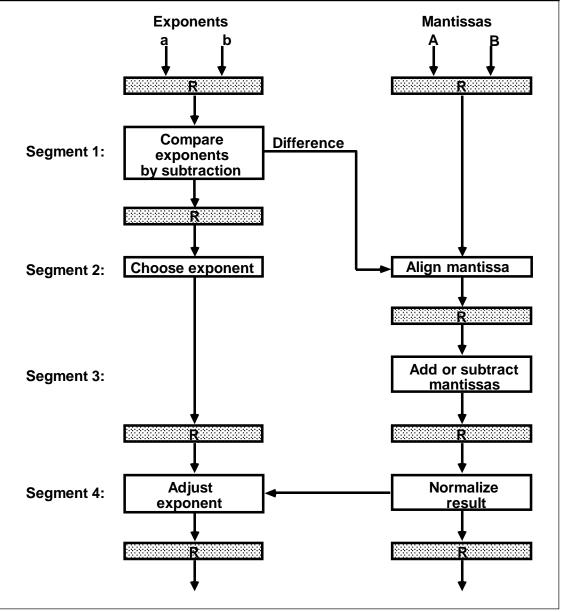

Computer Arithmetic: Addition and subtraction, multiplication Algorithms, Division Algorithms, Floating-point Arithmetic operations. Decimal Arithmetic unit, Decimal Arithmetic operations.

#### **MODULE-IV**

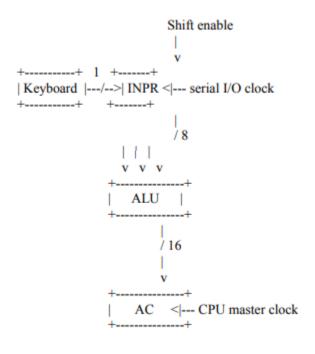

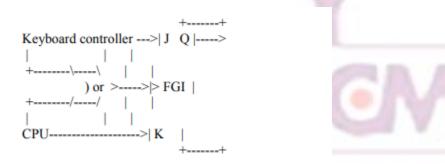

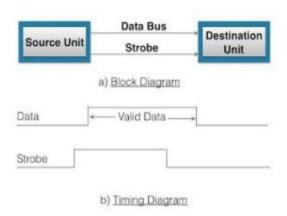

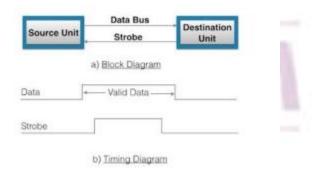

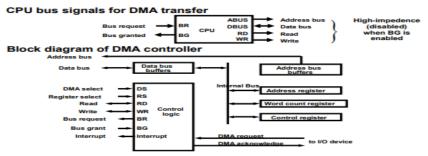

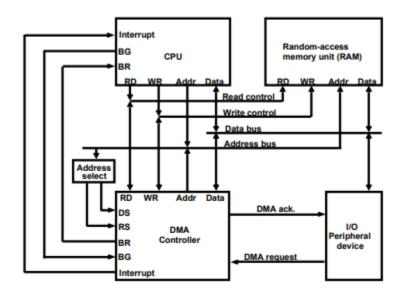

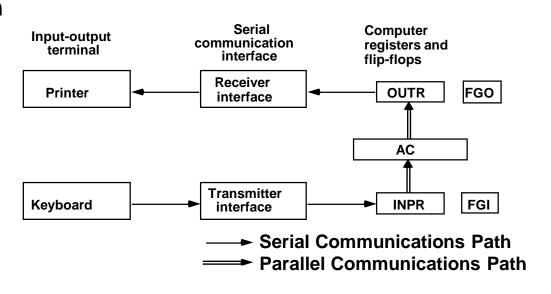

**Input-Output Organization:** Input-Output Interface, Asynchronous data transfer, Modes of Transfer, Priority Interrupt Direct memory Access.

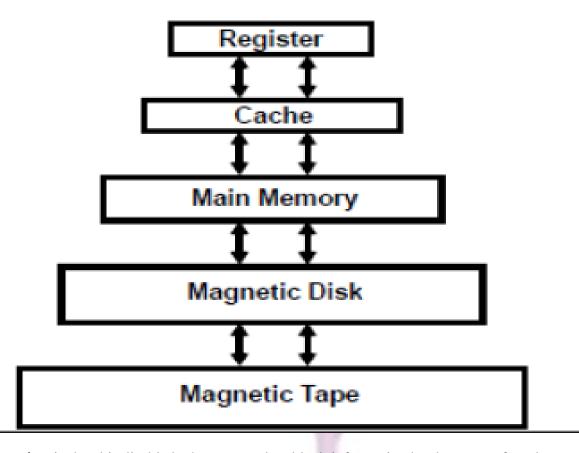

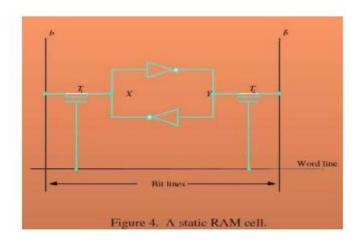

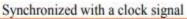

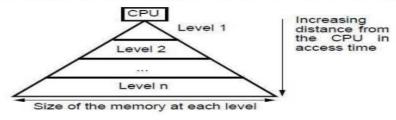

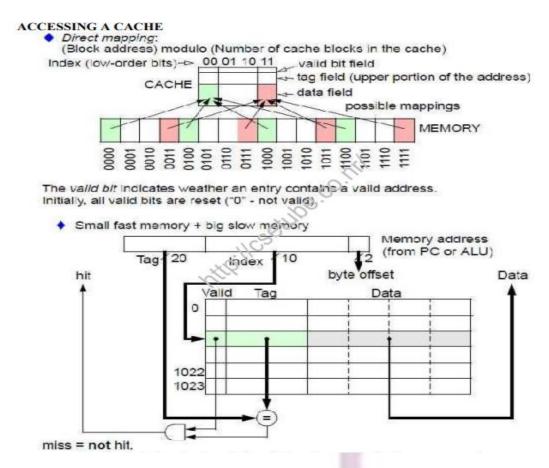

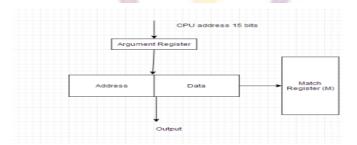

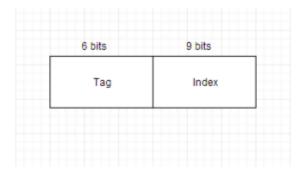

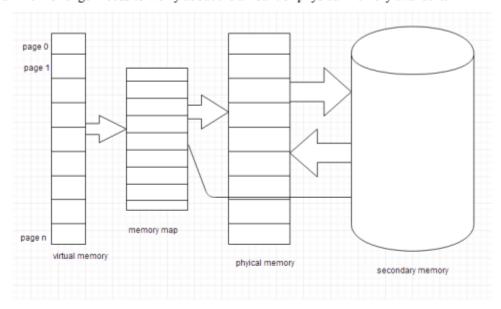

**Memory Organization:** Memory Hierarchy, Main Memory, Auxiliary memory, Associate Memory, Cache Memory.

#### **MODULE-V**

Reduced Instruction Set Computer: CISC Characteristics, RISC Characteristics.

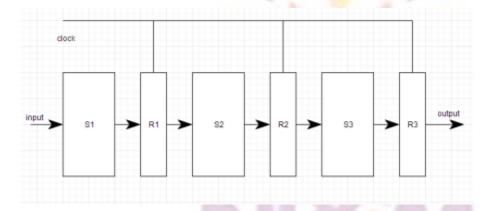

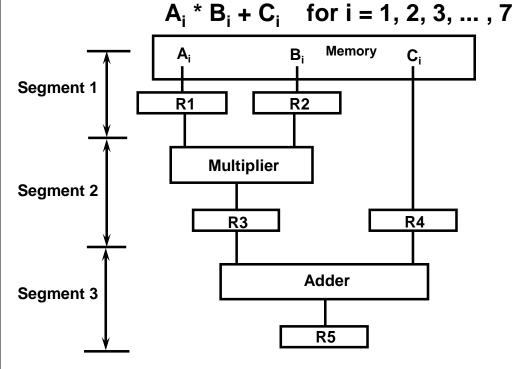

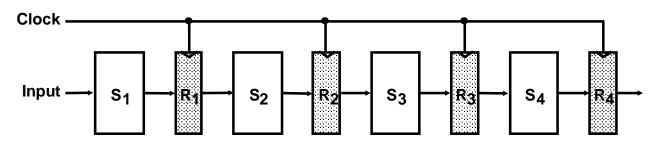

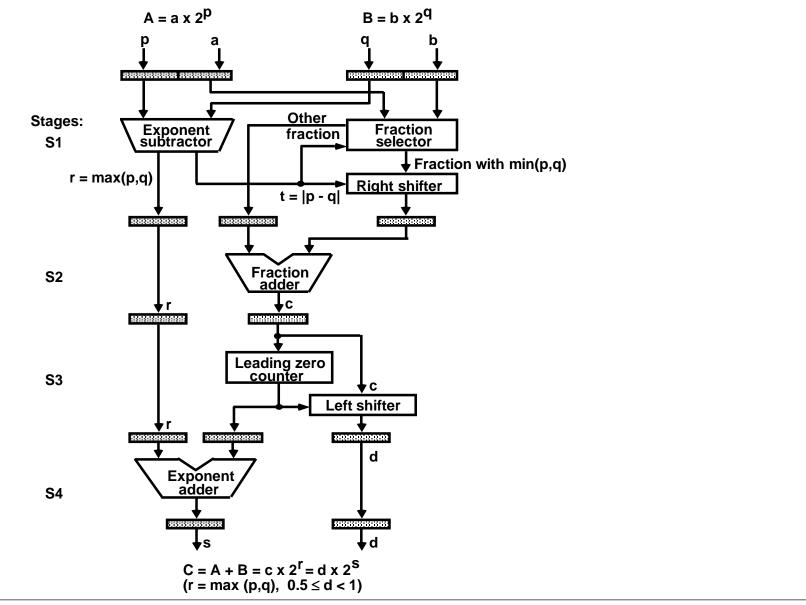

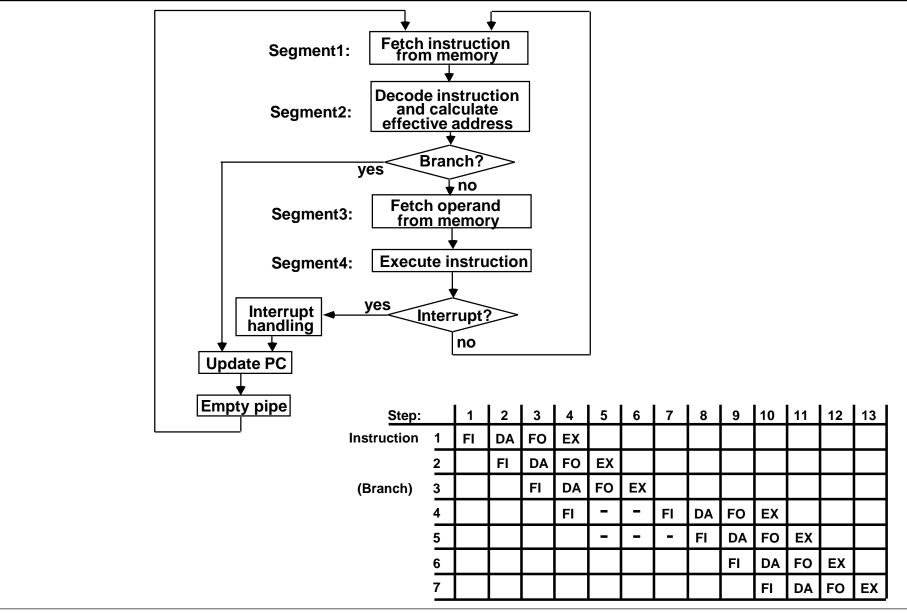

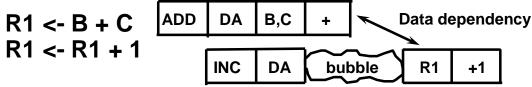

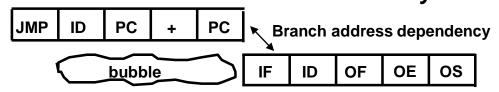

**Pipeline and Vector Processing:** Parallel Processing, Pipelining, Arithmetic Pipeline, Instruction Pipeline, RISC Pipeline, Vector Processing, Array Processor.

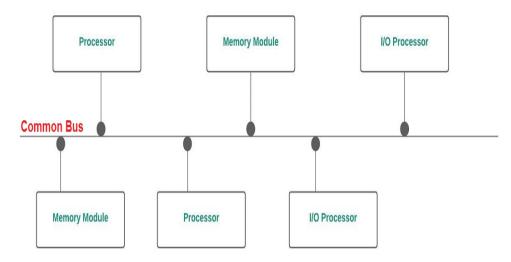

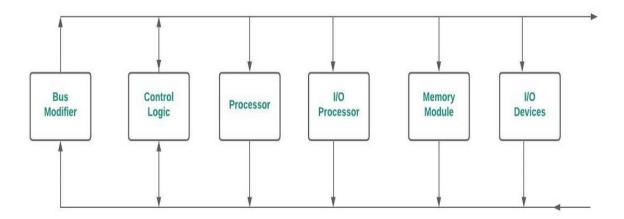

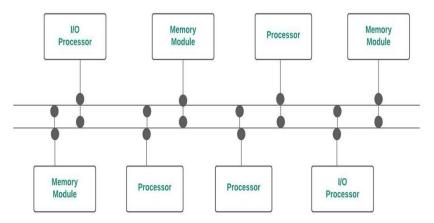

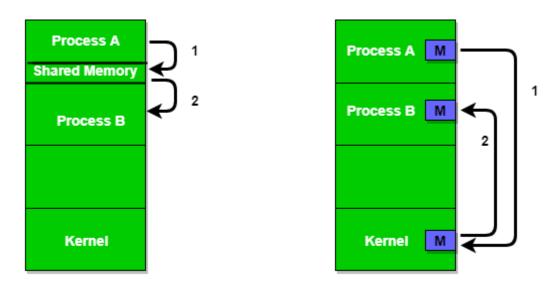

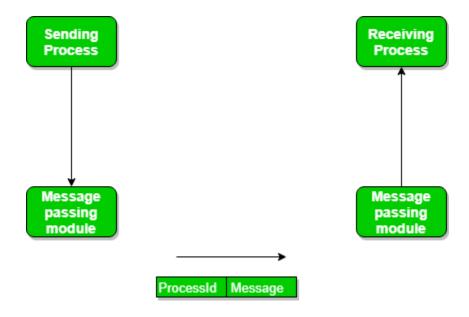

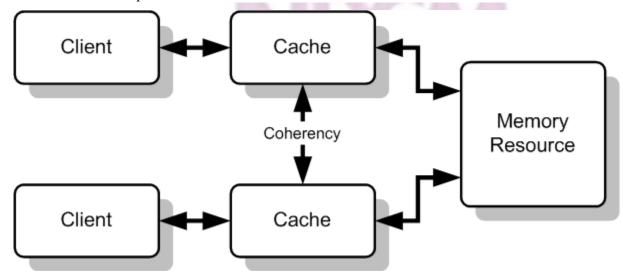

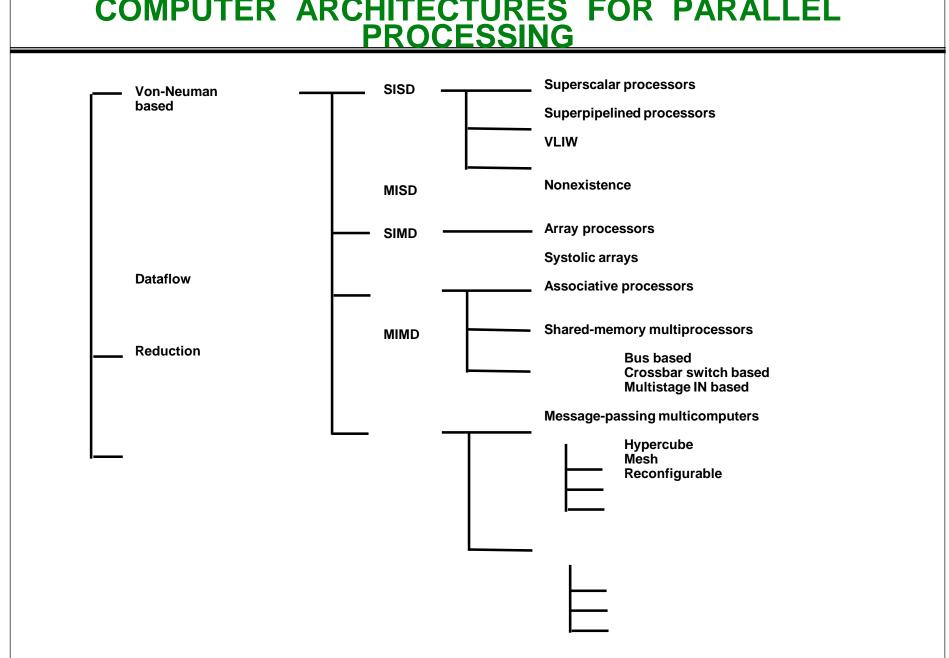

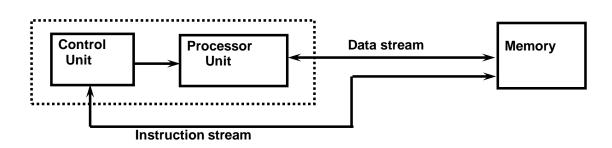

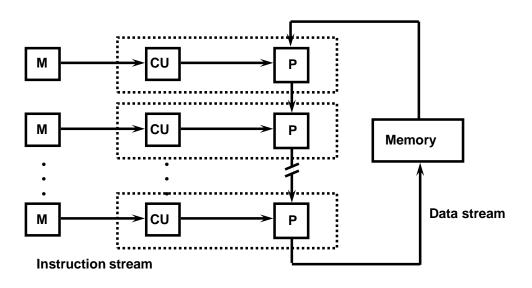

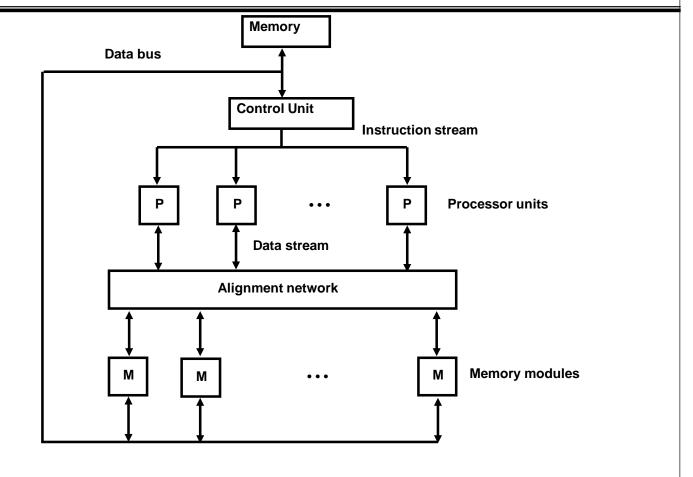

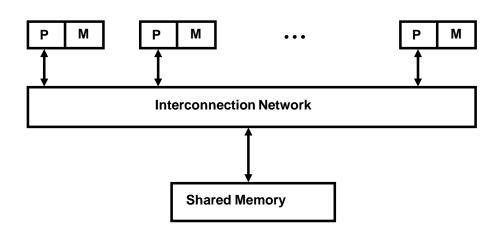

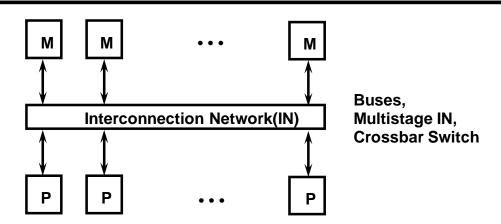

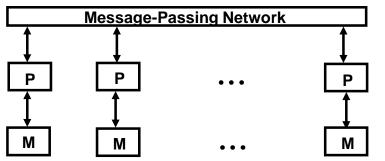

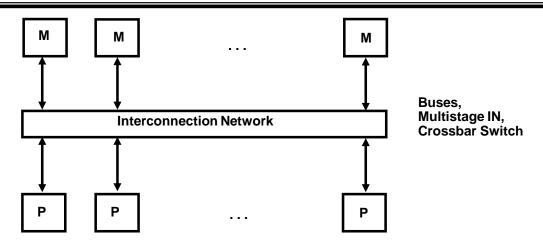

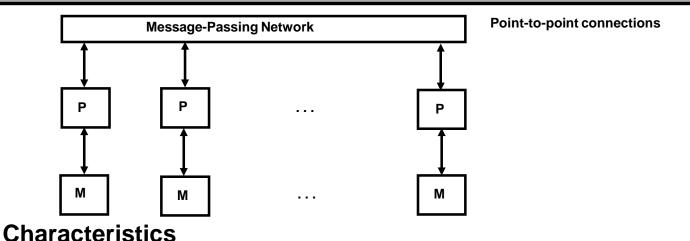

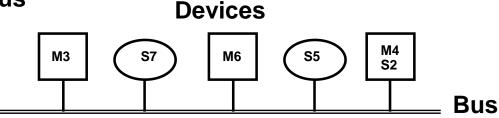

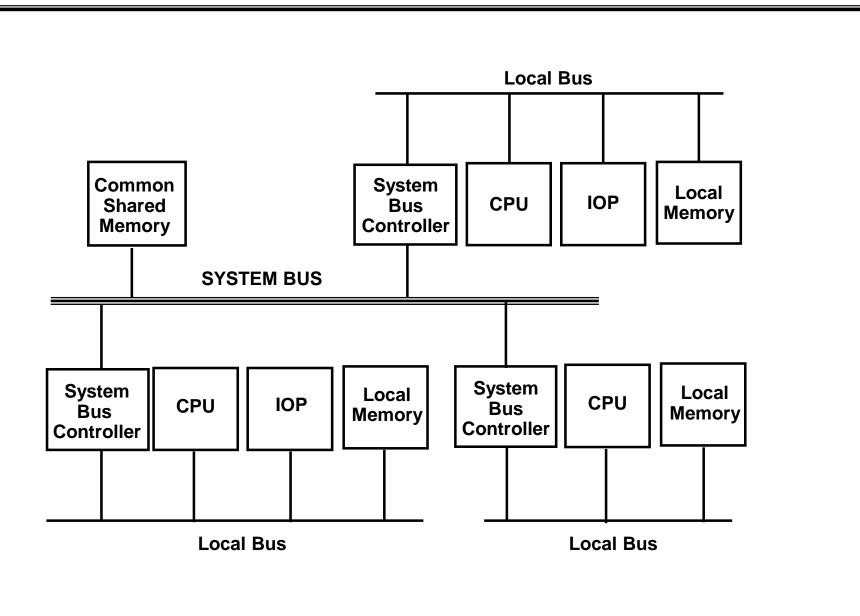

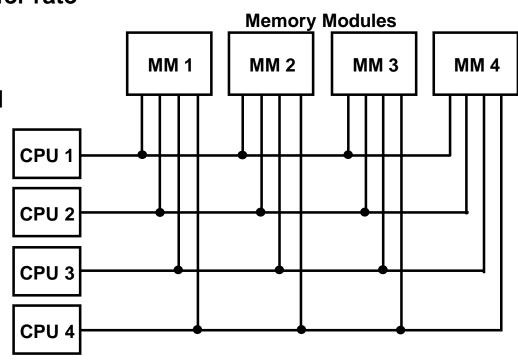

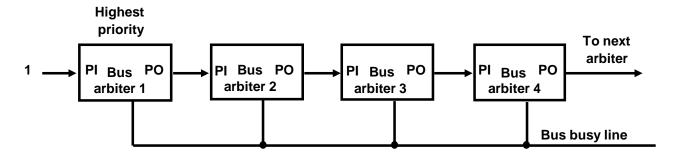

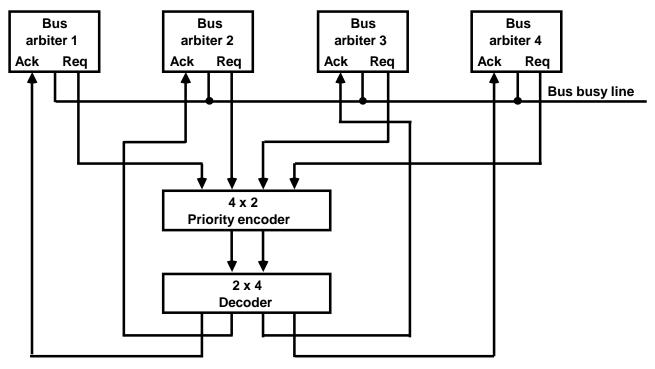

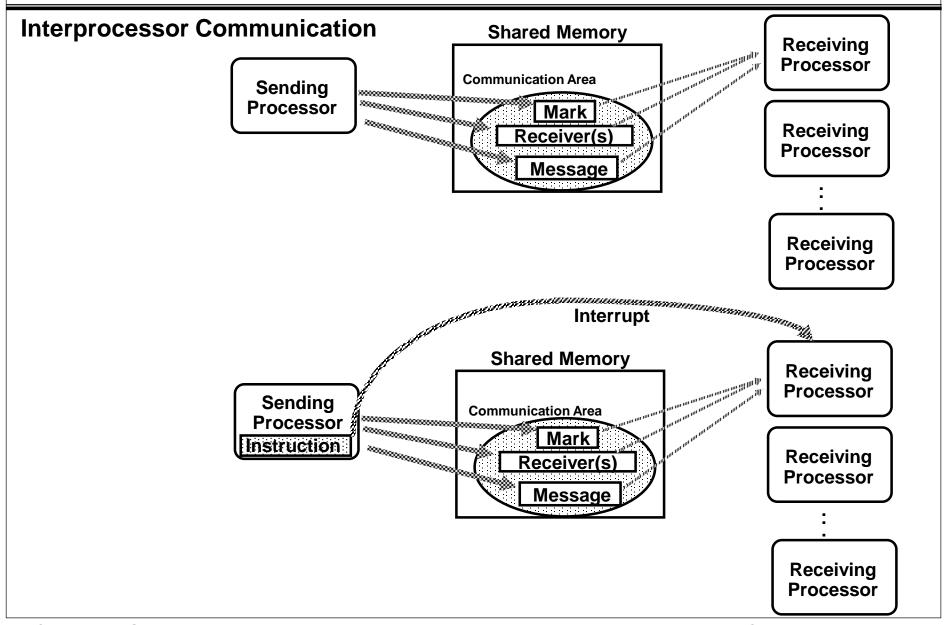

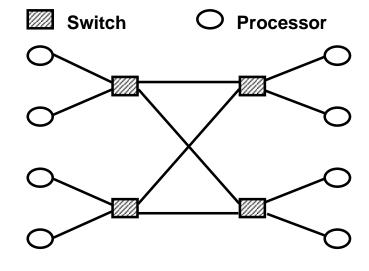

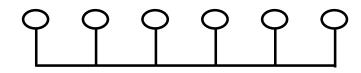

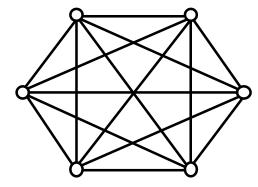

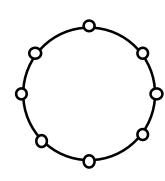

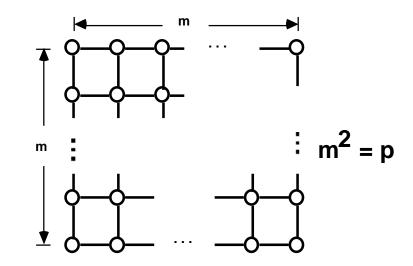

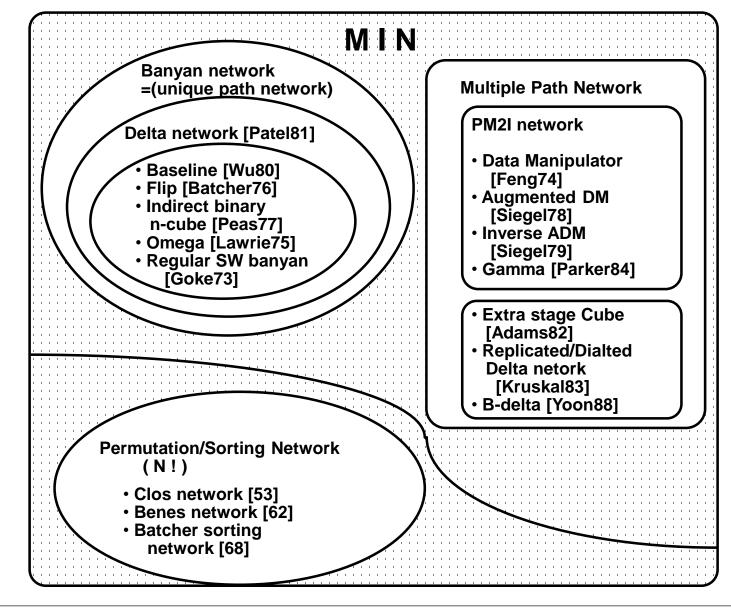

**MultiProcessors:** Characteristics of Multiprocessors, Interconnection Structures, Interprocessor arbitration, Interprocessor communication and synchronization, cache Coherence.

#### **TEXT BOOK:**

1. Computer System Architecture–M.MorisMano, Third Edition, Pearson/PHI.

#### **REFERENCE BOOKS:**

- 1. Computer Organization-Carl Hamacher, Zvonks Vranesic, Safea Zaky, V<sup>th</sup>Edition, McGrawHill.

- 2. Computer Organization and Architecture William Stallings Sixth Edition, Pearson/PHI.

- 3. Structured Computer Organization Andrew S.Tanenbaum, 4<sup>th</sup>Edition, PHI/Pearson.

# 4. List of COs (Action verbs as per Bloom's Taxonomy)

Course Name: (CS2104PC)

| Course<br>Code.CO<br>No | Course Outcomes (CO's)                                                                                               |  |  |  |  |  |  |  |  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

|                         | At the end of the course student will be able to                                                                     |  |  |  |  |  |  |  |  |

| CS2104PC                | Understand the basics of instructions sets and their impact on processor design.                                     |  |  |  |  |  |  |  |  |

|                         | Demonstrate an understanding of the design of the functional units of a digital computer system.                     |  |  |  |  |  |  |  |  |

|                         | Evaluate cost performance and design trade-offs in designing and constructing a computer processor including memory. |  |  |  |  |  |  |  |  |

| CS2104PC                | Design a pipeline for consistent execution of instructions with minimum hazards.                                     |  |  |  |  |  |  |  |  |

| CS2104PC                | Recognize and manipulate representations of numbers stored in digital computers                                      |  |  |  |  |  |  |  |  |

# Course Outcome (CO)-Program Outcome (PO) Matrix: (2022-2023) Course Name: CS2104PC

|       | PO1 | PO[2] | PO[3] | PO[4] | PO[5] | PO[6] | PO[7] | PO[8] | PO[9] | PO[10] | PO[11] | PO[12] |

|-------|-----|-------|-------|-------|-------|-------|-------|-------|-------|--------|--------|--------|

| CO[1] | 2   | 2     | 3     | 2     | 3     |       | V     |       |       |        | 2      | 2      |

| CO[2] | 2   | 3     | 1     | 1     | 2     |       |       |       |       |        | 3      | 2      |

| CO[3] | 1   | 2     | 2     | 2     | 1     |       |       |       |       |        | 1      | 3      |

| CO[4] | 2   | 1     | 3     | 2     | 2     |       | 10    | 7     | L A   |        | 2      | 2      |

| CO[5] | 2   | 2     | 1     | 3     | 3     | Bud   |       | • J.  | MΠ    |        | 1      | 2      |

# Mapping of course outcomes with PSO's

CO PSO Mapping (2022-2023)

|       | PSO[1] | PSO[2] | PSO[3] |

|-------|--------|--------|--------|

| CO[1] | 2      | 2      |        |

| CO[2] |        | 2      |        |

| CO[3] | 1      | 3      |        |

| CO[4] |        | 1      | 2      |

| CO[5] | 2      | 2      | 1      |

## **5. Nominal Rolls of the Students:**

II B.Tech – I Sem (2021 Batch):

CSE-A:

| CSE-A | •          |                                |

|-------|------------|--------------------------------|

| S.NO  | ROLL NO    | NAME OF THE STUDENT            |

| 1     | 21X01A0501 | AEDULLA NIKHIL                 |

| 2     | 21X01A0502 | ALAKUNTA ARJUN                 |

| 3     | 21X01A0503 | AKIRI HEMANTHSAI               |

| 4     | 21X01A0504 | AMBALA HARSHITH KUMAR          |

| 5     | 21X01A0505 | BANDARUPALLI SRI SAI HARSHITHA |

| 6     | 21X01A0506 | BADDAM PRASHANTH REDDY         |

| 7     | 21X01A0507 | BADDAM SHIVA NANDU REDDY       |

| 8     | 21X01A0508 | BADUGU SANJAY KUMAR            |

| 9     | 21X01A0509 | BANATHI NITHIN                 |

| 10    | 21X01A0510 | CHAKALA SUNIL                  |

| 11    | 21X01A0511 | CHALLA UDAY KIRAN              |

| 12    | 21X01A0512 | CHILUKURI SUNIL                |

| 13    | 21X01A0513 | DAMERA RATHAN PAUL             |

| 14    | 21X01A0514 | DHARAVATH GANESH               |

| 15    | 21X01A0515 | EDLA SAKETH                    |

| 16    | 21X01A0516 | GADARI ANUDEEP                 |

| 17    | 21X01A0517 | GADDE AKHIL                    |

| 18    | 21X01A0518 | GAJAGATTLA PRAVEEN             |

| 19    | 21X01A0519 | GANGARAMAINA NITHIN            |

| 20    | 21X01A0520 | GANGIDI AKANKSHA               |

| 21    | 21X01A0521 | GODEPALLY POOJA                |

| 22    | 21X01A0522 | JADA NAVEEN                    |

| 23    | 21X01A0523 | JANAGAMA VAMSHIKRISHNA         |

| 24    | 21X01A0524 | K SWETHA                       |

| 25    | 21X01A0525 | KALAKUNTLA BHANUPRASAD         |

| 26    | 21X01A0526 | KAMALAPURAM MEGHANA            |

| 27    | 21X01A0527 | KAMSALI SURYATEJA ACHARI       |

| 28    | 21X01A0528 | KAMUNI SAI SHASHINDRA          |

| 29    | 21X01A0529 | KOTTADA ELIZABETH RANI         |

| 30    | 21X01A0530 | KURELLI AKSHAYA                |

| 31    | 21X01A0531 | KURRA SATISH KUMAR             |

| 32    | 21X01A0532 | LACHULAGARI VAMSHI KRISHNA     |

| 33    | 21X01A0533 | LOKA PUNITH REDDY              |

| 34    | 21X01A0534 | M INDUSREE KATYAYANI           |

| 35    | 21X01A0535 | M SHIVARAM                     |

|       |            |                                |

| 36 | 21X01A0536 | MACHA MANOJ KUMAR            |

|----|------------|------------------------------|

| 37 | 21X01A0537 | MADDINENI HEMA SUNDAR        |

| 38 | 21X01A0538 | MADISHETTY GAYATHRI          |

| 39 | 21X01A0539 | MALGARI SAMPATH REDDY        |

| 40 | 21X01A0540 | MAMIDI RUCHITHA              |

| 41 | 21X01A0541 | M.V.SURYA                    |

| 42 | 21X01A0542 | MARRI MONIKA REDDY           |

| 43 | 21X01A0543 | N V MANOJ                    |

| 44 | 21X01A0544 | NAGULA RAVI KIRAN            |

| 45 | 21X01A0545 | NAGIGE SAITHEJA              |

| 46 | 21X01A0546 | ORAGANTI GANESH              |

| 47 | 21X01A0547 | P VIJAY                      |

| 48 | 21X01A0548 | PADALWAR SHRUTHI GOUD        |

| 49 | 21X01A0549 | PANTHAGANI RATHNAM           |

| 50 | 21X01A0550 | PANJALA SANGEETHA GOUD       |

| 51 | 21X01A0551 | PESSU SNEHITH REDDY          |

| 52 | 21X01A0552 | R VEENA                      |

| 53 | 21X01A0553 | S R M R T RATHNAKUMAR        |

| 54 | 21X01A0554 | SADANANDE SHRUTHI            |

| 55 | 21X01A0555 | SAKETH KANTE                 |

| 56 | 21X01A0556 | SANGU KRANTHI                |

| 57 | 21X01A0557 | TAHOORA RAFI                 |

| 58 | 21X01A0558 | THALLAPALLY MAHESH           |

| 59 | 21X01A0559 | TEKULAPALLY TARUN REDDY      |

| 60 | 21X01A0560 | UDGIRE SAMEER SHADUL         |

| 61 | 21X01A0561 | VEMIREDDY SRAVANTHI          |

| 62 | 21X01A0562 | VEMIREDDY LIKITHA REDDY      |

| 63 | 21X01A0563 | YELDI SRIVYBHAV              |

| 64 | 21X01A0564 | YANNE ADAM BASHA             |

| 65 | 21X01A0565 | YELLAIAHGARI ANUSHA          |

| 66 | 21X01A0566 | YEDDANDI MANISHA REDDY       |

| 67 | 21X01A0567 | YEDMALA PRATHYUSHA           |

| 68 | 22X05A0501 | BANJA POOJA                  |

| 69 | 22X05A0502 | BASAVARAJU DURGA BHANUPRASAD |

| 70 | 22X05A0503 | DEERAVATH GANESH NAYAK       |

# CSE- B

| 1 | 21X01A0568 | AMBIDI AKSHITHA     |

|---|------------|---------------------|

| 2 | 21X01A0569 | AMDHIPOOR VARUNGOUD |

| 3 | 21X01A0570 | AREPALLI MANOJ      |

| 4 | 21X01A0571 | BATHULA SAI KIRAN   |

| 5 | 21X01A0572 | BOOJALA SOURYA      |

| 6  | 21X01A0573   | BARKAM RISHIK                |

|----|--------------|------------------------------|

| 7  | 21X01A0574   | BHEEMANATHI HARINI           |

| 8  | 21X01A0575   | BHUKYA JASVANTH              |

| 9  | 21X01A0576   | BODA DIVYASRI                |

| 10 | 21X01A0577   | CHALLA NAGALAKSHMI           |

| 11 | 21X01A0578   | CHINTHALAPELLY SAHASRA REEDY |

| 12 | 21X01A0579   | CHIRRA BALAKRISHNA REDDY     |

| 13 | 21X01A0580   | DRAKSHARAM SOWMYA            |

| 14 | 21X01A0581   | DUNGU SUBROTO CHAKRAVARTHY   |

| 15 | 21X01A0582   | GOGULA LAXMI PRASANNA        |

| 16 | 21X01A0583   | GOPISETTI VIVEK SAI          |

| 17 | 21X01A0584   | GOSULA RAJKUMAR              |

| 18 | 21X01A0585   | GUDA MEGHANA                 |

| 19 | 21X01A0586   | GOLI SAI KIRAN               |

| 20 | 21X01A0587   | GOLKONDA PRANAY              |

| 21 | 21X01A0588   | ISLAVATH ABHISHEK NAYAK      |

| 22 | 21X01A0589   | JANGA MAHESH                 |

| 23 | 21X01A0590   | JARPULA SRAVAN KUMAR         |

| 24 | 21X01A0591   | KANNABATHULA VENKAT SAI      |

| 25 | 21X01A0592   | KANUGANTI HARI PRIYA         |

| 26 | 21X01A0593   | KANUKULA STANLY              |

| 27 | 21X01A0594   | KARINGU SHIVASHANKAR         |

| 28 | 21X01A0595   | KARINGULA KAVYA SRI          |

| 29 | 21X01A0596   | KASHISH PAREKH               |

| 30 | 21X01A0597   | KOMMULA MARUTHI              |

| 31 | 21X01A0598   | KOMPELLA VENKATA             |

| 31 | 21/(01/105/0 | SUBRAHMANYA SHARAT CHANDRA   |

| 32 | 21X01A0599   | KONDE CHANDANA               |

| 33 | 21X01A05A0   | MAMIDIPALLY ASHWITHA         |

| 34 | 21X01A05A1   | MANDHA NAVEEN                |

| 35 | 21X01A05A2   | MANTRI SOWMYA                |

| 36 | 21X01A05A3   | MASKURI SINDHU               |

| 37 | 21X01A05A4   | MIDDELA GOPI SAGAR           |

| 38 | 21X01A05A5   | MOHAMMAD SHAREEF             |

| 39 | 21X01A05A6   | MOHAMMED NAUSHAD             |

|    |              | MOHIUDDIN                    |

| 40 | 21X01A05A7   | MATHYA HEPSIBHA              |

| 41 | 21X01A05A8   | MUKUL REDDY ANAGANDULA       |

| 42 | 21X01A05A9   | NARENDRAPURAPU TEJASWI       |

| 43 | 21X01A05B0   | NEDUNURI AVINASH             |

| 44 | 21X01A05B1   | NAKIRI VENKATESH             |

| 45 | 21X01A05B2   | OTARKAR SAI KUMAR            |

| 46 | 21X01A05B3 | PASHAM VAMSHI                |

|----|------------|------------------------------|

| 47 | 21X01A05B4 | PATHIREDDY ABINAYA           |

| 48 | 21X01A05B5 | PATNAM VAMSHI                |

| 49 | 21X01A05B6 | PODILAPU HARADEEP            |

| 50 | 21X01A05B7 | POWER NAVEEN                 |

| 51 | 21X01A05B8 | RAPARTHI SAI KIRTHI          |

| 52 | 21X01A05B9 | RAVALKOL PAVAN KUMAR         |

| 53 | 21X01A05C0 | SAMALA VYSHNAVI              |

| 54 | 21X01A05C1 | SAMPANGI VILAKAR             |

| 55 | 21X01A05C2 | SANGAM SRINIDHI              |

| 56 | 21X01A05C3 | SATTI GOWTHAM RAVINDRA REDDY |

| 57 | 21X01A05C4 | THATI BHARATH                |

| 58 | 21X01A05C5 | TUNGALA NEERAJ               |

| 59 | 21X01A05C6 | THALLURI CHAKRAVARTHI        |

| 60 | 21X01A05C7 | VEMIREDDY RAM DINESH REDDY   |

| 61 | 21X01A05C8 | VELPULA ABHINAV              |

| 62 | 21X01A05C9 | VADLA LAXMI NARASIMHA        |

| 63 | 21X01A05D0 | VELMA SAI CHARAN REDDY       |

| 64 | 21X01A05D1 | YEMULA SRICHARAN             |

| 65 | 21X01A05D2 | YENAGANDULA RAHUL            |

| 66 | 21X01A05D3 | YELLAMMALA RAMYA             |

| 67 | 21X01A05D4 | YERRA SANJANA                |

| 68 | 22X05A0504 | DUSSA GANESH                 |

| 69 | 22X05A0505 | GATTU SAI PRAKASH            |

| 70 | 22X05A0506 | GOLLAPALLI DINESH KUMAR GOUD |

# CSE- C

| S.NO | ROLL NO    | NAME OF THE STUDENT       |

|------|------------|---------------------------|

| 1    | 21X01A05D5 | ANEDLA AKSHITHA           |

| 2    | 21X01A05D6 | ANUMAS MOUNIKA            |

| 3    | 21X01A05D7 | ATLA SRUJANA              |

| 4    | 21X01A05D8 | BADDIPADIGA DURGA BHAVANI |

| 5    | 21X01A05D9 | BOIN RAMU                 |

| 6    | 21X01A05E0 | BOLLEPELLY VIGNESH        |

| 7    | 21X01A05E1 | BURSU KAMESHWARA RAO      |

| 8    | 21X01A05E2 | BURUJU SIDDARTHA REDDY    |

| 9    | 21X01A05E3 | CHEDE RUCHITHA            |

| 10   | 21X01A05E4 | CHILUVERI JAISH           |

| 11   | 21X01A05E5 | CHITAMANENI SAI TANUJ     |

| 12   | 21X01A05E6 | CHITYALA KOUSHIK REDDY    |

| 13   | 21X01A05E7 | CHUKKA RAJENDRA           |

| 14 | 21X01A05E8 | DYAGARI PRIYA               |

|----|------------|-----------------------------|

| 15 | 21X01A05E9 | GUGULOTH MADHU CHANDANA     |

| 16 | 21X01A05F0 | GUMPULA NAVEEN              |

| 17 | 21X01A05F1 | GUNDE RAKESH                |

| 18 | 21X01A05F2 | GUNDEBOINA SNEHA            |

| 19 | 21X01A05F3 | GUNTAKULAM SAI NIKITHA      |

| 20 | 21X01A05F4 | GOURU SAI PAVAN             |

| 21 | 21X01A05F5 |                             |

| 22 | 21X01A05F6 | JILAKARA ADITHYA            |

| 23 | 21X01A05F7 | JAKKULA GANGAMANI           |

| 24 | 21X01A05F8 | KASUKURTHI SUPRIYA          |

| 25 | 21X01A05F9 | KONDAIAHGARI MANISHA        |

| 26 | 21X01A05G0 | KOTAGIRI PRANAY KUMAR       |

| 27 | 21X01A05G1 | KOTTALA RAJITHA             |

| 28 | 21X01A05G2 | KURRA ASRITHA               |

| 29 | 21X01A05G3 | KUSUMA RAMYA                |

| 30 | 21X01A05G4 | KAGGA GOPICHAND             |

| 31 | 21X01A05G5 | KATARI BHAVANI PRASAD VARMA |

| 32 | 21X01A05G6 | KATTA ASHRITHA REDDY        |

| 33 | 21X01A05G7 | MUMMANENI SREETHARATHNAM    |

| 34 | 21X01A05G8 | MOULIK PATEL                |

| 35 | 21X01A05G9 | MUDAVATH SANTHOSH           |

| 36 | 21X01A05H0 | MUDDADA RAVI SANKAR         |

| 37 | 21X01A05H1 | MULGI RUDRAKSHA             |

| 38 | 21X01A05H2 | MUNFED ALI                  |

| 39 | 21X01A05H3 | MUTHYAM NIKSHITHA           |

| 40 | 21X01A05H4 | MUTTUM UMESH                |

| 41 | 21X01A05H5 | NIMMAKANTI MADHUSAGAR       |

| 42 | 21X01A05H6 | NIRUDI DINESH               |

| 43 | 21X01A05H7 | NIRUDI VAISHNAVI            |

| 44 | 21X01A05H8 | NIMMALA MANOJ               |

| 45 | 21X01A05H9 | BOLLA SRIKAR                |

| 46 | 21X01A05I0 | PAYYAVULA DINESH KUMAR      |

| 47 | 21X01A05I1 | PERUPOGU SANDEEP            |

| 48 | 21X01A05I2 | PS VENNALA VEDASHINEE       |

| 49 | 21X01A05I3 | PUPPALA RISHIKESH           |

| 50 | 21X01A05I4 | ROUTHU PRABHAKAR            |

| 51 | 21X01A05I5 | SHAIK AKASH                 |

| 52 | 21X01A05I6 | SHAIK SOHEL                 |

| 53 | 21X01A05I7 | SIDDIQUA TABASSUM           |

| 54 | 21X01A05I8 | SIRIMALLA SIRI CHANDANA     |

| 55 | 21X01A05I9 | SIRIPURAM VINAY KUMAR                    |

|----|------------|------------------------------------------|

| 56 | 21X01A05J0 | SHIVARATHRI VIGNESHWAR                   |

| 57 | 21X01A05J1 | SNEHA TRIPATHY                           |

| 58 | 21X01A05J2 | TURKANI LALAPPA                          |

| 59 | 21X01A05J3 | THOTAKURA SHRAVYA                        |

| 60 | 21X01A05J4 | KADMURI KAUSHIK KUMAR VARMA              |

| 61 | 22X05A0507 | GSANDEEP                                 |

| 62 | 22X05A0508 | KAGNALI NANDINI                          |

| 63 | 22X05A0509 | KAITHALAPURAM HEMANTH                    |

| 64 | 22X05A0510 | KATAM ASHWINI                            |

| 65 | 22X05A0511 | KORPATHI HEMALATHA                       |

| 66 | 22X05A0512 | MAHESHWARAM JITHENDHER                   |

| 67 | 22X05A0513 | PODILA NAVA BH <mark>A</mark> RATH KUMAR |

| 68 | 22X05A0514 | R SAI VARDHAN                            |

| 69 | 22X05A0515 | RODDA BHA <mark>NU</mark> PRASAD         |

| 70 | 22X05A0516 | S MANJUNADHA                             |

| 71 | 22X05A0517 | SATHU AJAY REDDY                         |

| 72 | 22X05A0518 | SHAIK SURAJ BABA                         |

| 73 | 22X05A0519 | SINAMGARAM CHANDU YADAV                  |

| 74 | 22X05A0520 | THUPAKULA VAMSHI YADAV                   |

6. TIME TABLE (2022-2023)

# NARSIMHA REDDY ENGINEERING COLORS DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING TIME TABLE

CLASS: II -YEAR CSE -A I-SEM (2022-2023) CLASS INCHARGE: Dr. N. SRINIVAS RAO

ROOM NUMBER: 111

WEF: 28-09.2022

II YEAR INCHARGE: Dr. N.

| . SRINIVAS | RAO |

|------------|-----|

| 6          | 7   |

| CLI      | i i                 | 2                    | 3                    | 4                   | 12:50PM - | 5                  | 6                  | 7<br>3:20PM - |

|----------|---------------------|----------------------|----------------------|---------------------|-----------|--------------------|--------------------|---------------|

| HOUR/DAY | 9:30AM -<br>10:20AM | 10:20AM -<br>11:10AM | 11:10AM -<br>12:00PM | 12.00PM-<br>12.50PM | 1:40PM    | 1:40PM -<br>2:30PM | 2:30PM -<br>3:20PM | 4.10PM        |

| MON      | ADE                 | COA                  | C++                  | C++                 |           |                    | DS LAB             |               |

| TUE      | COA                 | COA                  | COSM                 | COSM                | L         | DS                 | ADE                | ADE           |

| WED      | COSM                | DS                   | DS                   | COA                 | U         |                    | C++ LAB            |               |

| THU      | C++                 | DS                   | DS DS COA N C ITW    |                     |           |                    | ITWS LAB           |               |

| FRI      | C++                 |                      | ADE LAB              |                     |           | COSM               | COSM               | SPORTS        |

| SAT      |                     | GENDER SE            | NSITIZATION          |                     |           | LIB                | RARY               | SPORTS        |

| S.NO | COURSE CODE | COURSE TITLE                           | FACULTY                               |

|------|-------------|----------------------------------------|---------------------------------------|

| SINO |             |                                        | K.ANNAMMA                             |

| 1    | EC2101ES    | Analog and Digital Electronics         | Dr. U. MOHAN SRINIVAS                 |

| 2    | CS2102PC    | Data Structures                        | G.SHANDHIYA RANI                      |

| 3    | MA2103BS    | Computer Oriented Statistical Methods  | Dr. N. SRINIVAS RAO                   |

| 4    | CS2104PC    | Computer Organization and Architecture |                                       |

| 5    | CS2105PC    | Object Oriented Programming using C++  | D. GNANAPRASANNA                      |

| 6    | EC2106ES    | Analog and Digital Electronics Lab     | K.ANNAMMA                             |

| 7    |             | Data Structures Lab (Room no. 007)     | Dr. N. SRINIVAS RAO, DR. R.RAJAGOPAL, |

| 7    | CS2107PC    | Data Sudetules Late (Room no. 99.7)    | P.RAMPRASAD, S. SHAKINA               |

|      |             |                                        | A BARKATHULLA, P.RAMPRASAD            |

| 8    | CS2108PC    | IT Workshop lab (Room No, 107)         | D. GNANAPRASANNA, S. SHAKINA, DR.     |

| 9    | CS2109PC    | C++ Programming Lab (Room no. 108)     | R.RAJAGOPAL                           |

|      |             |                                        | S. SHAKINA, P.RAMPRASAD               |

| 10   | MC2002*     | Gender Sensitization Lab               | S. SHAKINA, P.KAWITKASAD              |

un Time Table Coordinator(s)

AGH.

# NARSIMHA REDDY ENGINEERING COLLEGE DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING TIME TABLE

CLASS: II -YEAR CSE -B I-SEM (2022-2023)

ROOM NUMBER: 112

WEF: 28.09.2022

CLASS INCHARGE: Dr. R.RAJAGOPAL

II YEAR INCHARGE: Dr. N. SRINIVAS RAO

| CLIN     | D.J. H. C. L.       |                      |                      |                     |           | 5        | 6        | 1        |

|----------|---------------------|----------------------|----------------------|---------------------|-----------|----------|----------|----------|

|          | 1                   | 2                    | 3                    | 4                   | 12:50PM - | 1:40PM - | 2:30PM - | 3:20PM - |

| HOUR/DAY | 9:30AM -<br>10:20AM | 10:20AM -<br>11:10AM | 11:10AM -<br>12:00PM | 12.00PM-<br>12.50PM | 1:40PM    | 2:30PM   | 3:20PM   | 4.10PM   |

|          |                     |                      | DS                   | DS                  |           | ADE      | C++      | C++      |

| MON      | COSM                | COSM                 | Do                   |                     | -         | COA      | COA      | COSM     |

| TUE      | C++                 |                      | C++ LAB              |                     |           | COA      |          |          |

|          | -                   | COA                  | COA C++ C++          |                     |           |          | ITWS LAB |          |

| WED      | ADE                 | COA                  |                      | 1                   | N<br>C    | COA      | DS       | SPORTS   |

| THU      | COSM                |                      | ADE LAB              |                     | Н         | COA      | DS       |          |

| 1110     |                     |                      | 14900                | DS                  |           |          | DS LAB   |          |

| FRI      | ADE                 | ADE                  | COSM                 | 100000              |           | LIB      | RARY     | SPORTS   |

| CAT      |                     | GENDER SE            | NSITIZATION          |                     |           | 13115    |          |          |

| S.NO | COURSE                 | COURSE TITLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | FACULTY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|